# JK Chrome | Employment Portal

# Rated No.1 Job Application of India

Sarkari Naukri Private Jobs Employment News Study Material Notifications

JK Chrome

www.jkchrome.com | Email : contact@jkchrome.com

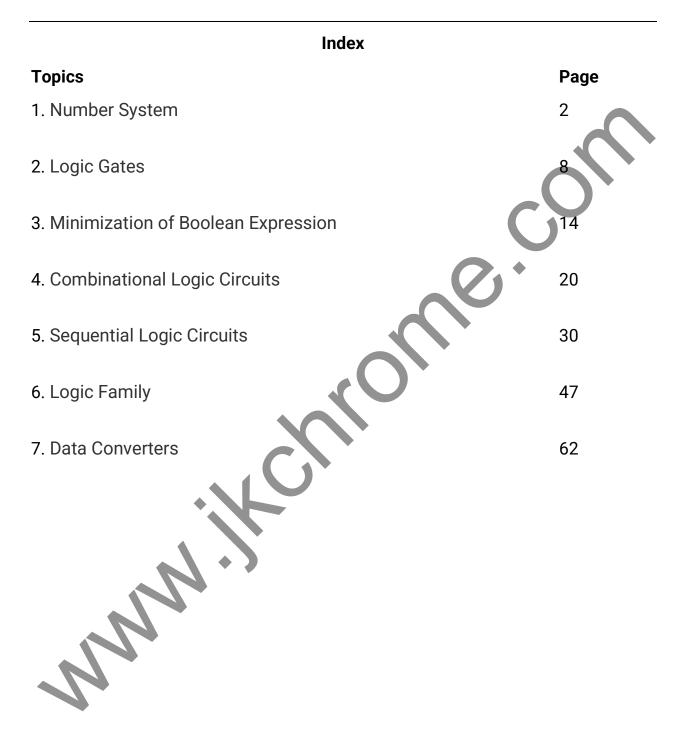

# **Digital Electronics**

#### **Number System**

#### **Binary Codes**

- Binary codes are codes that are represented in a binary system with modification from original ones.

- In general, N bits can represent up to  $2^N$  distinct values.

- Conversely, to represent a range of M values, the number of bits required is.

| 1 bit       | →             | represents up to 2 values (0, 1)                                   |              |

|-------------|---------------|--------------------------------------------------------------------|--------------|

| 2 bits      | $\rightarrow$ | represents up to 4 values (00, 01, 10, 11)                         |              |

| 3 bits      | $\rightarrow$ | represents up to 8 values (000, 001, 010, 011, 100, 101, 110, 111) | G            |

| 4 bits      | $\rightarrow$ | represents up to 16 values (0000, 0001,                            | 0.*          |

| 32 values   | $\rightarrow$ | 0010,, 1110, 1111)<br>requires 5 bits                              | Ø            |

| 40 values   | $\rightarrow$ | requires 6 bits                                                    |              |

| 64 values   | $\rightarrow$ | requires 6 bits                                                    |              |

| 100 values  | $\rightarrow$ | requires 7 bits                                                    | *            |

| 1024 values | $\rightarrow$ | requires 10 bits                                                   | Logic Family |

|             |               |                                                                    |              |

- The *base* or *radix* of a number system is the number of digits present. The decimal numeral system has a base or radix of 10, where the set of 10 symbols (digits) is {0, 1, 2, 3, 4, 5, 6, 7, 8, 9}. The weights are in powers of ten.

- In general, a bases-b number  $(a_n a_{n-1} \dots a_0 \dots f_1 f_2 \dots f_m)_b$  has the value  $(a_n \times b^n) + (a_{n-1} \times b^{n-1}) + \dots + (a_0 \times b^0) + (f_1 \times b^{-1}) + (f_2 \times b^{-2}) + \dots + (f_m \times b^{-m})$

- Weighted Binary System: Weighted binary codes are those which obey the positional weighting principles, each position of a number represents a specific weight.

# e.g., 8421, 2421, 5211

- Sequential Code: A code is said to be sequential when two subsequent codes, seen as numbers in the binary representation, differ by one. The 8421 and excess-3 codes are sequential, whereas the 2421 and 5211 codes are not.

- Non-weighted Codes: non-weighted codes are codes that are not positionally weighted. That is each position within the binary number is not assigned a fixed value.

• **Reflective Code:** A code is said to be reflective when the code for 9 is a complement for the code for 0 and so is for 8 and 1 codes, 7 and 2, 6 and 3, 5 and 4. Codes 2421, 5211, and excess-3 are reflective, whereas the 8421 code is not.

#### **BCD (Binary Coded Decimal)**

It is a straight assignment of the binary equivalent. To encode a decimal number using the common BCD encoding. Each decimal digit is stored in a 4-bit number.

| Decimal | 0      | 1       | 2                 | 3                   | 4          | 5       | 6     | 7     | 8    | 9    |

|---------|--------|---------|-------------------|---------------------|------------|---------|-------|-------|------|------|

| BCD     | 0000   | 0001    | 0010              | 0011                | 0100       | 0101    | 0110  | 0111  | 1000 | 1001 |

| • BCE   | ) enco | ding fo | or num            | ber 12 <sup>.</sup> | 7 woul     | d be    |       | 0     | +    |      |

| 127     |        |         |                   |                     |            |         | ~     |       |      |      |

| (0001   | 0010   | 0111)   | $\rightarrow BCI$ | D equiv             | alent      | of 127  |       |       |      |      |

| wher    | eas th | e pure  | binary            | numb                | er wou     | ld be ( | 01111 | 111)2 |      |      |

| • BCI   | )      |         |                   |                     | $\bigcirc$ |         |       |       |      |      |

| Add (   | 148 +  | 157) =  | ?                 | C                   |            |         |       |       |      |      |

| 148     | _      | BCD     |                   | 000                 | )1         | 01      | 00    | 1     | 000  |      |

| 157     | 1.0    | BCD     | $\rightarrow$     | 000                 | )1         | 01      | 01    | 0     | 111  |      |

|         |        | $\sim$  | • 7               | 001                 | 0          | 10      | 01    | 1     | 111  |      |

|         |        |         | -                 |                     | 1-         | 01      | 10    | 0     | 110  |      |

|         | $\sim$ |         |                   | 001                 | 11         |         | 14    | -10   | 0101 |      |

|         |        |         |                   |                     |            | 10      | 000   | _     |      |      |

| Answe   | r      |         | 1                 | 1                   | 3          |         | 0     |       | 5    |      |

|         |        |         |                   |                     |            |         |       |       |      |      |

When the sum of 2 digits is greater than or equal to 9, then we need to add 6 i.e., 0110.

• 2421 Code

This is a weighted code, its weights are 2, 4, 2, and 1. A decimal number is represented in 4-bit form and the total 4 bits weight is

2 + 4 + 2 + 1 = 9.

Hence, the 2421 code represents the decimal numbers from 0 to 9.

| Decimal | 0 | 1 | 2  | 3  | 4   | 5    | 6    | 7    | 8    | 9  |

|---------|---|---|----|----|-----|------|------|------|------|----|

| 2421    | 0 | 1 | 10 | 11 | 100 | 1011 | 1100 | 1101 | 1110 | um |

#### • Excess-3 Code

Excess-3 is a non-weighted code used to represent decimal numbers. The code derives its name from the fact that each binary code is the corresponding 8421 code plus 0011 (3).

e.g.,

| Decimal | 8421 | Excess-3           |

|---------|------|--------------------|

| 8       | 1000 | 1000 + 0011 = 1011 |

| 6       | 110  | 0110 + 0011 = 1001 |

#### Gray Code

This is a variable weighted code and is cyclic. This means that it is arranged so that every transition from one value to the next value involves only onebit Change.

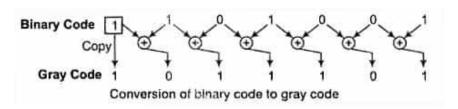

#### Binary to Gray Code Conversion

- 1. Write down the number in binary codes.

- 2. The Most Significant Bit (MSB) of the gray code will be the same as the MSB of binary code.

- 3. Perform XOR operation on MSB and next bit to the MSB in a binary number.

- 4. Repeat step 3 till all bits of the binary number have been XO Red, the resultant code is the gray code equivalent to the binary code.

#### • Gray Code to Binary Conversion

- 1. Start with the MSB of gray coded numbers.

- 2. Copy this bit as the MSB of the binary number.

- 3. Now, perform the Ex-OR operation of this bit with the next bit of the binary number.

- 4. Repeat step 3 till all bits of gray coded numbers have been used in the XOR operation. The resultant number is the binary equivalent of the gray number.

**Gray Code** Cop Binary Code Conversion of gray code to binary code

#### Complements

- Complements are used in a digital computer system for simplifying the subtraction operation and for logical manipulation.

- There are two types of complements for each baser system,

- 1. The r's complement

- 2. The (r' 1)'s complement

- The r's Complement

Given a positive number N with baser with an integer part of n digits. The r's complement of N is defined as  $r^n - N$  for N  $\neq 0$  and 0 for N = 0.

e.g., 10's complement of (25.639)<sub>10</sub> is (10<sup>2</sup> - 25.639)

100 - 25.639 = 74 - 361, here the number of digits in integer part is 2

means n = 2

• The (r – 1)'s Complement

Given, a positive number N in baser with an integer part of n digits and a fraction part of m digits, the (r - 1)'s complement of N is defined as  $r^n - r^{-m} - N$ .

- 1's complement of  $(52520)_{10}$  is  $(10^5 1 52520)$ = 99999 - 52520 = 47479 Because number of integer part is 5, so r<sup>n</sup> = 10<sup>5</sup> and no fractional part is Present' so r<sup>-m</sup> = 10<sup>-0</sup> = 1

- 1's complement of  $(0.3267)_{10}$  is  $(10^0 10^{-4} 0.3267)$ = 1 - 0.0001 - 0.3267 = 0.9999 - 0.3267 = 0.6732 No integer part, so  $10^n = 10^0 = 1$

- 1's complement of  $(101100)_2$  is  $(2^6 2^0)_{10} (101100)_2$ =  $(64 - 1)_{10} - (101100)_2$ =  $(63)_{10} = (101100)_2$ = 111111 - 101100 = 010011

- Key Points

- $520 \rightarrow$  Here, n = 3, but (052)  $\rightarrow$  here n = 2.

- In the latter example, 0 is of no significance.

# Representation of Integers

- The are three possible ways to represent a number

- 1. Signed magnitude method

- 2. 1's complement method

- 3. 2's complement method

- Signed Magnitude Method

- The number is divided into two parts, one is the sign bit and another part for magnitude, In the example we are using the 5-bit register to represent -6 and +6.

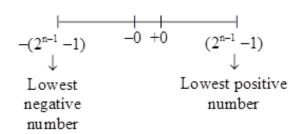

• The range of Number For n bit register, MSB will be a sign bit and (n - 1) bits will be the magnitude.

- Key Points

- The drawback of the signed magnitude method is that 0 will be having 2 different representations one will be 10000 i.e., -0 and the other one will be 00000 + 0.

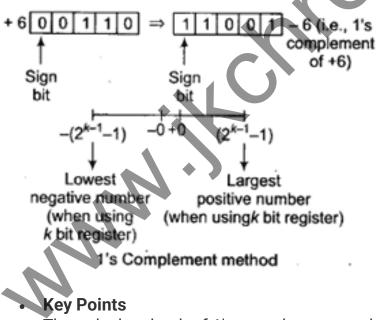

#### **1's Complement Method**

- Positive numbers are represented in the same way as in the signmagnitude method. If the number is negative, then it is represented using 1's complement method. For this, we first need to represent the number with a positive sign and then take 1's complement of this number.

- e.g., Suppose we are using a 5-bit register. The representation of -6 will be as below.

The only drawback of 1's complement method is that there are two different representations for zero, one is -0, and the other is +0.

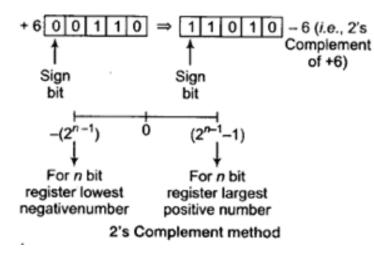

#### 2's Complement Method

• Positive numbers are represented in the same way as in sign-magnitude. For representing a negative number, we take 2's complement of the corresponding positive number.

# **Properties of 2's Complement**

- 2's complement representation allows the use of binary arithmetic operations on signed integers, yielding the current 2's complement result.

- **Positive Numbers** Positive 2's complement numbers are represented as the simple binary.

- **Negative Numbers** Negative 2's complement numbers are represented as the binary number that when added to a positive number of the same magnitude equals zero.

# Logic Gates

A logic gate is an idealised or physical device implementing a Boolean function, that is, it performs a logical operation in one or more logical inputs and produces a single logical output.

The logic gates can be classified as

- NOT, AND, OR are basic gates.

- NAND, NOR are universal gates.

- EXOR, EXNOR are an arithmetic circuit or code converter or comparators.

# NOT Gate (Inverter)

#### Truth Table for NOT Gate:

| Input | Output $Y = \overline{A}$ |  |

|-------|---------------------------|--|

| 0     | 1                         |  |

| 1     | 0                         |  |

**Circuit Symbol for NOT Gate:**

**AND Gate:**

**Truth Table for AND Gate:**

| Inputs |   | Output |

|--------|---|--------|

| Α      | В | Y = AB |

| 0      | 0 | 0      |

| 0      | 1 | 0      |

| 1      | 0 | 0      |

| 1      | 1 | 1      |

Circuit Symbol for AND Gate:

A٥ AB Bo

Properties of AND logic:

- 1. Commutative Law: AB = BA

- 2. Associative Law: ABC = (AB) C = (AC)B = A(BC)

OR Gate:

Truth Table:

| Inputs |   | Output  |

|--------|---|---------|

| Α      | В | Y = A + |

|        |   | В       |

| 0      | 0 | 0       |

| 0      | 1 | 1       |

| 1      | 0 | 1       |

| 1      | 1 | 1       |

**Circuit Symbol for OR Gate:**

$$\begin{array}{c} A \\ B \\ \hline \end{array} \end{array} \begin{array}{c} & & \\ \end{array} \begin{array}{c} & & \\ & & \\ \end{array} \begin{array}{c} & & \\ & & \\ & & \\ \end{array} \begin{array}{c} & & \\ & & \\ & & \\ \end{array} \begin{array}{c} & & \\ & & \\ & & \\ \end{array} \begin{array}{c} & & \\ & & \\ & & \\ \end{array} \begin{array}{c} & & \\ & & \\ & & \\ \end{array} \begin{array}{c} & & \\ & & \\ & & \\ \end{array} \begin{array}{c} & & \\ & & \\ & & \\ \end{array} \begin{array}{c} & & \\ & & \\ & & \\ \end{array} \begin{array}{c} & & \\ & & \\ & & \\ \end{array} \begin{array}{c} & & \\ & & \\ & & \\ \end{array} \begin{array}{c} & & \\ & & \\ & & \\ \end{array} \begin{array}{c} & & \\ & & \\ & & \\ \end{array} \begin{array}{c} & & \\ & & \\ & & \\ \end{array} \begin{array}{c} & & \\ & & \\ & & \\ \end{array} \begin{array}{c} & & \\ & & \\ & & \\ \end{array} \begin{array}{c} & & \\ & & \\ & & \\ \end{array} \begin{array}{c} & & \\ & & \\ & & \\ \end{array} \begin{array}{c} & & \\ & & \\ & & \\ \end{array} \begin{array}{c} & & \\ & & \\ & & \\ \end{array} \begin{array}{c} & & \\ & & \\ & & \\ \end{array} \begin{array}{c} & & \\ & & \\ & & \\ \end{array} \begin{array}{c} & & \\ & & \\ & & \\ \end{array} \begin{array}{c} & & \\ & & \\ & & \\ \end{array} \begin{array}{c} & & \\ & & \\ & & \\ \end{array} \begin{array}{c} & & \\ & & \\ & & \\ \end{array} \begin{array}{c} & & \\ & & \\ \end{array} \begin{array}{c} & & \\ & & \\ & & \\ \end{array} \begin{array}{c} & & \\ & & \\ & & \\ \end{array} \begin{array}{c} & & \\ & & \\ \end{array} \begin{array}{c} & & \\ & & \\ & & \\ \end{array} \begin{array}{c} & & \\ & & \\ \end{array} \end{array}$$

#### **Properties of OR logic:**

- 1. Commutative Law: A + B = B + A

- 2. Associative Law: (A + B + C) = (A + B) + C = A + (B + C)

#### NAND Gate:

Truth Table:

| Α | B | Y   |

|---|---|-----|

| 0 | 0 | 1   |

| 0 | 1 |     |

| 1 | 0 | + 1 |

| 1 | 1 | 0   |

**Circuit Symbol for NAND Gate:**

$$A \leftarrow D \leftarrow Y = \overline{AB}$$

NOR Gate:

Truth Table:

| Α | В | $Y = \left(\overline{A + B}\right)$ |

|---|---|-------------------------------------|

| 0 | 0 | 1                                   |

| 0 | 1 | 0                                   |

| 1 | 0 | 0                                   |

| 1 | 1 | 0                                   |

**Circuit Symbol for NOR Gate:**

$$A \xrightarrow{B} Y = (A + B)$$

• NOR gate follows commutative law but not follow associative law

EXOR Gate:

Truth Table:

| Inputs |   | Output         |

|--------|---|----------------|

| Α      | В | <b>Y</b> = A⊕B |

| 0      | 0 | 0              |

| 0      | 1 | 1              |

| 1      | 0 | 1              |

| 1      | 1 | 0              |

**Circuit Symbol for EXOR Gate:**

$$A \longrightarrow B \longrightarrow Y = A \oplus B = \overline{AB} + A\overline{B}$$

**Properties of EXOR Logic:**

- Enable input = 0

- Disable input = 1

- It is also called stair case switch.

- It is widely used in parity generation and detection.

- When both the inputs are different, then output becomes high or logic 1.

- When both the inputs are same, then output becomes low or logic 0.

#### Note:

$$A\oplus A=0; A\oplus \overline{A}=1; \, A\oplus 0=A; A\oplus 1=\overline{A}$$

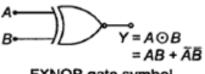

#### **EX-NOR Gate:**

#### Truth Table:

| Inputs | 5 | Output           |

|--------|---|------------------|

| Α      | В | <b>Y</b> = A ⊙ B |

| 0      | 0 | 1                |

| 0      | 1 | 0                |

| 1      | 0 | 0                |

| 1      | 1 | 1                |

Circuit Symbol for EX-NOR Gate:

EXNOR gate symbol

#### **Properties of EXNOR Gate:**

- Enable input = 1

- Disable input = 0

- When both the inputs are same, then output .becomes high or logic 1.

- When both the inputs are different, then output becomes low or logic 0.

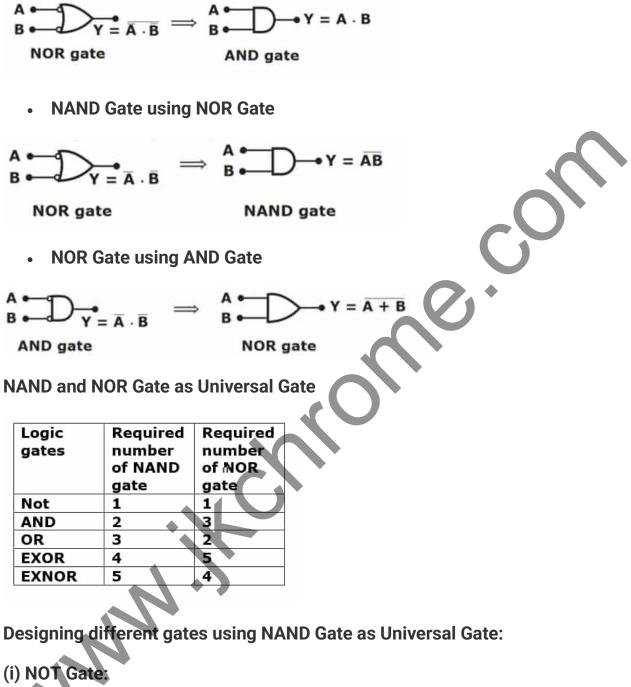

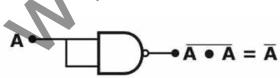

#### Logic Gate Conversions

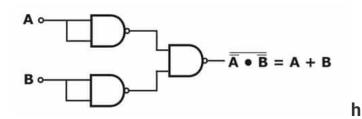

• OR Gate using NAND Gate:

$$A \bullet B \bullet Y = A \cdot B \Rightarrow B \bullet Y = A + B$$

NAND gate

OR gate

• AND Gate using NOR Gate:

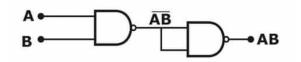

(ii) AND Gate:

(iii) OR Gate:

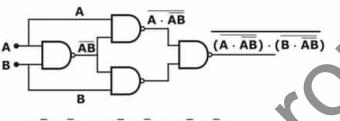

(iv) EXOR Gate:

$A(\overline{A} + \overline{B}) + B(\overline{A} + \overline{B}) = A\overline{B} + \overline{A}\underline{B}$

# **Minimization of Boolean Expression**

# 1. Introduction to Boolean Algebra

- Boolean algebra is an algebraic structure defined on a set of elements together with two binary operators (+) and (.)

- A **variable** is a symbol, for example, 'A' used to represent a logical quantity, whose value can be **0** or **1**.

- The **complement of a variable** is the inverse of a variable and is represented by the variable over bar.

• A **literal** is a variable or the complement of a variable.

#### Boolean Value

$_{\circ}$  The value of Boolean variable can be either 1 or 0.

- Boolean Operators: There are three basic Boolean operators

- $_{\circ}$   $\,$  AND ( ) operator  $\,$

- $\circ$  OR (+) operator

- NOT operator

#### 2. Duality

• If an expression contains only the operations AND, OR and NOT. Then, the dual of that expression is obtained by replacing

each AND by OR,

each OR by AND,

all occurrences of 1 by 0,

all occurrences of 0 by 1.

The principle of duality is useful in determining the complement of a function.

- Logic expression: (x •y' •z) + (x •y •z') + (y •z) + 0

- Duality of above logic expression is:  $(x + y' + z) \cdot (x + y + z') \cdot (y + z) \cdot 1$

#### **Boolean Function:**

- Any Boolean functions can be formed from binary variables and the Boolean operators.

- For a given value of the variable, the function can take only one value either 0 or 1.

- A Boolean function can be shown by a truth table. To show a function in a truth table we need a list of the 2<sup>n</sup> combinations of 1's and 0's of the 'n' binary variables and a column showing the combinations for which the function is equal to 1 or 0. So, the table will have 2<sup>n</sup> rows and columns for each input variable and tile final output.

- A function can be specified or represented in any of the following ways:

- A truth table

- A circuit

- A Boolean expression

- SOP (Sum Of Products)

- POS (Product of Sums)

- Canonical SOP

- Canonical POS

- Important Boolean operations over Boolean values:

| 0  | • 0 = 0           |

|----|-------------------|

| 1  | • 1 = 1           |

| 0  | • $1 = 1 • 0 = 0$ |

| 0' | = 1               |

| 1  | + 1 = 1           |

| 0  | + 0 = 0           |

| 1  | +0=0+1=1          |

| 1' | = 0               |

#### 3. Basic Theorems

| Law/Theorem      | Law of Addition                       | Law of Multiplication                                                                             |

|------------------|---------------------------------------|---------------------------------------------------------------------------------------------------|

| Identity Law     | x + 0 = x                             | $x \cdot 1 = x$                                                                                   |

| Complement Law   | x + x' = 1                            | $\mathbf{x} \cdot \mathbf{x}' = 0$                                                                |

| Idempotent Law   | x + x = x                             | $\mathbf{X} \cdot \mathbf{X} = \mathbf{X}$                                                        |

| Dominant Law     | x + 1 = 1                             | $\mathbf{x} \cdot 0 = 0$                                                                          |

| Involution Law   | (x')' = x                             |                                                                                                   |

| Commutative Law  | x + y = y + x                         | $\mathbf{x} \cdot \mathbf{y} = \mathbf{y} \cdot \mathbf{x}$                                       |

| Associative Law  | x+(y+z) = (x+y)+z                     | $\mathbf{x} \cdot (\mathbf{y} \cdot \mathbf{z}) = (\mathbf{x} \cdot \mathbf{y}) \cdot \mathbf{z}$ |

| Distributive Law | $x \cdot (y+z) = x \cdot y+x \cdot z$ | $x+y \cdot z = (x+y) \cdot (x+z)$                                                                 |

| Demorgan's Law   | $(x+y)' = x' \cdot y'$                | $(\mathbf{x} \cdot \mathbf{y})' = \mathbf{x}' + \mathbf{y}'$                                      |

| Absorption Law   | $x + (x \cdot y) = x$                 | $\mathbf{x} \cdot (\mathbf{x} + \mathbf{y}) = \mathbf{x}$                                         |

#### Important Theorems used in Simplification

#### **NOT-Operation theorem:**

$$\overline{\overline{A}} = A$$

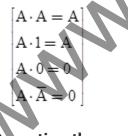

**AND-Operation theorem:**

**OR-Operation theorem:**

$$\begin{bmatrix} A + A = A \\ A + 0 = A \\ A + 1 = 1 \\ A + \overline{A} = 1 \end{bmatrix}$$

#### **Distribution theorem:**

• A + BC = (A + B)(A + C)

#### Others:

$A + \overline{A}B = A + B$  $A + \overline{A}\overline{B} = A + \overline{B}$  $\overline{A} + AB = \overline{A} + B$  $\overline{A} + A\overline{B} = \overline{A} + \overline{B}$

- 0

- Consensus Theorem: This theorem is used to eliminate redundant term. It is applicable only when a boolean function contains three variables. Each variable used two times. Only one variable is complemented or uncomplemented. Then the related terms so that complemented or uncomplemented variable is the answer.

- $AB + \overline{B}C + AC = \overline{B}C + AB$  $\overline{A}B + \overline{B}C + \overline{A}C = \overline{B}C + \overline{A}\overline{B}$

- $AB + \overline{A}C + BC = AB + \overline{A}C$

- $A\overline{B} + AC + BC = A\overline{B} + BC$

#### 4. MinTerm & MaxTerm

- Minterm:

- Each product term is known as a minimum term that contains all the variables used in a function.

- A minterm is also called a canonical product term.

- A minterm is a product term, but a product term may or may not be a minterm.

- Maxterm:

- Each sum term is known as a maximum term that contains all of the variables used in the function.

- A **maxterm** is a sum term of all variables in which each variable is either in complemented form or in uncomplemented form.

- A maxterm is also called a **canonical sum term**.

- A maxterm is a sum term, but a sum term may or may not be a maxterm.

- The following are examples of product term, minterm, sum term, and maxterm for a function of three variables a, b, and c:

- product terms: a, ac, b'c, abc, a'bc, a'b'c', ...

- minterms: ab'c, abc, a'b'c, a'b'c', ...

- sum terms: a, (a+b), (b+c), (a'+b), (a'+b'), ...

- maxterms: (a+b+c), (a+b'+c), (a'+b'+c'), ...

#### Representations of Minterm and Maxterm:

| x | y | z | Minterm | Minterm<br>Notation | Maxterm      | Maxterm<br>Notation |

|---|---|---|---------|---------------------|--------------|---------------------|

|   |   |   |         | Notation            |              |                     |

| 0 | 0 | 0 | x'y'z'  | <u>m0</u>           | x + y + z    | M0                  |

| 0 | 0 | 1 | x'y'z   | <i>m1</i>           | x + y + z'   | M1                  |

| 0 | 1 | 0 | x'yz'   | <i>m</i> 2          | x + y' + z   | M2                  |

| 0 | 1 | 1 | x'yz    | <i>m3</i>           | x + y' + z'  | M3                  |

| 1 | 0 | 0 | x y' z' | m4                  | x' + y + z   | M4                  |

| 1 | 0 | 1 | x y'z   | m5                  | x' + y + z'  | M5                  |

| 1 | 1 | 0 | x y z'  | <u>m6</u>           | x' + y' + z  | <i>M</i> 6          |

| 1 | 1 | 1 | xyz     | <i>m7</i>           | x' + y' + z' | M7                  |

- Note: With' n' variables maximum possible minimum and maximum terms

= 2<sup>n</sup>

- With' n' variables maximum possible logic expression = 2<sup>2<sup>\*</sup></sup>

# 5. SOP & POS

- **SOP (Sum of Product):** A **sum** of product expression is two or more OR functions of AND functions.

- SOP expression is used when output becomes logic 1.

- Example:  $ABC + \overline{ABC} + AB\overline{C}$

- **POS (Product of Sum):** It is the AND function of two or more OR function.

- POS expression is used when output is logic '0'.

• Example.

$$(A + B + C) \cdot (A + \overline{B} + C) \cdot (\overline{A} + \overline{B} + \overline{C})$$

• Example: SOP and POS Equivalences for function F and Its Inverse F'.

$$\begin{array}{c|c} F & x'yz + xy'z + xyz' + xyz \\ \hline \\ Inverse \\ F' & x'y'z' + x'y'z + x'yz' + xy'z' \\ \hline \\ F' & x'y'z' + x'y'z + x'yz' + xy'z' \\ \hline \\ \end{array}$$

6. Duality Theorem

- To convert positive logic into negative logic and *vice-versa, a* dual function is used.

- Change each AND sign by OR sign and vice versa ( $\leftrightarrow$  +)

- Complement any 0 or I appearing in expression.

- Keep variable as it is.

- Example:

$\mathbf{A} \cdot \overline{\mathbf{B}} \cdot \mathbf{C} + \overline{\mathbf{A}} \cdot \mathbf{B} \cdot \mathbf{C} + \mathbf{A} \mathbf{B} \overline{\mathbf{C}} \xleftarrow{dual} (\mathbf{A} + \overline{\mathbf{B}} + \mathbf{C}) \cdot (\overline{\mathbf{A}} + \mathbf{B} + \mathbf{C}) \cdot (\mathbf{A} + \mathbf{B} + \overline{\mathbf{C}})$

# 7. Minimization of Boolean Expressions

The following two approaches can be used for simplification of a Boolean expression:

- Algebraic method (using Boolean algebra rules)

- Karnaugh map method

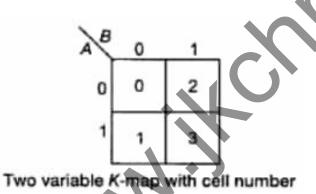

Representation of K-map: With n-variable Karnaugh-map, there are 2<sup>n</sup> cells

• 2 -variable K Map:

• 3 -variable K Map:

#### • 4 -variable K Map:

NOTE: Once the Karnaugh map has been populated with 1s, 0s and Xs as specified the only task that remains is to group adjacent terms of the same state (usually 1) in groups of 2 raised to any rational power, i.e. 1, 2, 4, 8, 16, 32, 64 and so on. The larger the group the simpler the final expression. It is also possible for groups to overlap. This is often done to achieve a larger group size, hence simplifying the final expression.

#### Minimization Procedure of Boolean Expression using K-map

- Construct a K-map.

- Find all groups of horizontal or vertically adjacent cells that contain 1.

- Each group must be either rectangular or square with 1, 2, 4, 8, or 16 cells.

- Each group should be as large as possible.

- Each cell with 1 on the K-map must be covered at least once. The same

- the cell can be included in several groups if necessary.

- Select the least number of groups so as to cover all the 1's.

- Adjacency applies to both vertical and horizontal borders.

- Translate each group into a product term. (Any variable whose value changes from cell to cell drops out from the term)

- Sum all the product terms.

- Note: Don't care conditions can be used to provide further simplification of a Boolean Expression.

#### **Combinational Logic Circuits**

#### **1. Designing Combinational Circuits**

The steps to design combinational circuits are as the following

- Understand the problem

- Find the required number of input and output variables

- Construct a truth table using the relationship between the input and output

- Obtain the Boolean function or the logical expression from the truth table using Karnaugh Map.

- Draw a logic circuit based on the obtained logical expression.

#### 2. Arithmetic Circuits

Arithmetic circuits are used to perform addition and subtraction. Binary adder performs binary addition and binary subtractor performs binary subtraction.

#### Classification of Adder:

- Half Adder

- Full Adder

#### **Classification of Subtractor:**

- Half Subtractor

- Full Subtractor

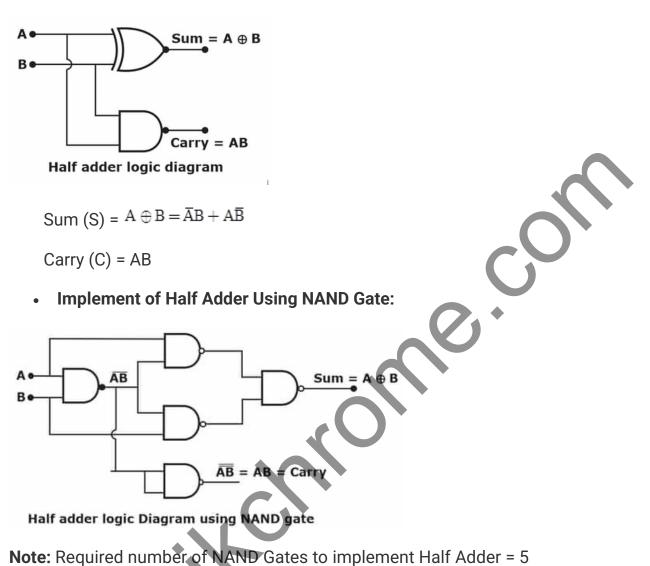

# Half Adder

This circuit is used for addition of two one bit numbers.

# • The truth table of Half Adder:

| Inp | uts | Ou      | tput      |

|-----|-----|---------|-----------|

| Α   | B   | Sum (S) | Carry (C) |

| 0   | 0   | 0       | 0         |

| 0   | 1   | 1       | 0         |

| 1   | 0   | 1       | 0         |

| 1   | 1   | 0       | 1         |

• Half adder circuit:

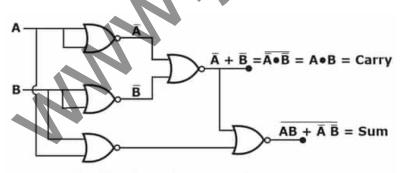

Implement of Half Adder Using NOR Gate:

Half adder logic diagram using NOR gate

Note: Required number of NOR Gates to implement Half Adder = 5

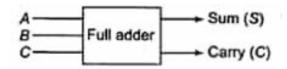

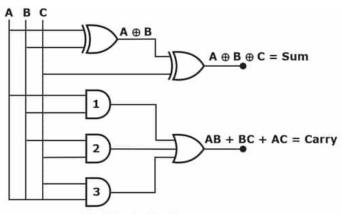

#### Full Adder

A full adder is a combinational logic circuit that performs the arithmetic sum of three input bits. It consists of three inputs and two outputs.

• The truth table for Full Adder:

|   | INPUT |      | OUI | PUT  |

|---|-------|------|-----|------|

| Α | B     | C(i) | S   | C(0) |

| 0 | 0     | 0    | 0   | 0    |

| 0 | 0     | 1    | 1   | 0    |

| 0 | 1     | 0    | 1   | 0    |

| 0 | 1     | 1    | 0   | 1    |

| 1 | 0     | 0    | 1   | 0    |

| 1 | 0     | 1    | 0   | 1    |

| 1 | 1     | 0    | 0   | 1    |

| 1 | 1     | 1    | 1   | 1    |

Full Adder Truth Table

- The logic diagram of Full Adder:

- Sum (S) =  $A \oplus B \oplus C = \overline{A}\overline{B}C + \overline{A}B\overline{C} + A\overline{B}\overline{C} + ABC$

Carry  $(C_0) = AB + BC + AC$

Full adder logic diagram

- A full adder = 2 Half adder + 1 OR Gate

- Required minimum number of NAND gate to implement FA=9

- Required minimum number of NOR gate to implement FA = 9

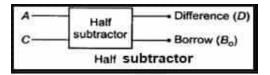

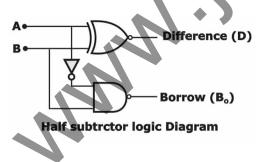

#### Half Subtractor

- Logic Diagram of Half Subtractor:

- Difference (D)

- Borrow (B<sub>0</sub>) =

- To implement half subtractor the total number of NAND/NOR are required

= 5

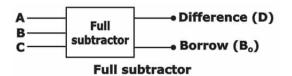

#### **Full Subtractor**

It is a combinational logic circuit that performs subtraction involving three bit namely minuend bit, subtrahend bit and borrows from the previous stage

- Difference (D) =  $A \oplus B \oplus C$

- Borrow  $(B_0) = \overline{A}B + \overline{A}C + BC = \overline{A}B + (\overline{A \oplus B}) \cdot C$

- A full subtractor = 2 half subtractor + 1 OR gate

- To implement full subtractor of NAND/NOR gates are required =

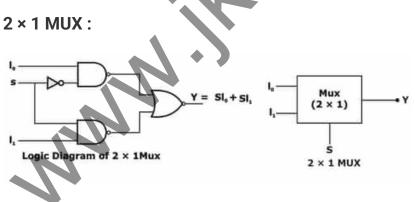

# 3. Multiplexer (MUX)

- It is a combinational circuit that selects binary information from one of the many input lines and directs it to a single output line.

- The selection of a particular input line is controlled by a set of selection lines.

- MUX is also called: Many to one, Data selector, Universal circuit, or Parallel data serial.

- Multiplexing means transmitting a large number of information units over a smaller number of channels or lines. It is abbreviated as MUX.

- There are 2<sup>*n*</sup> input lines and *n* selection lines whose bit combinations determine which input is selected.

$m = 2^n$  implies  $n = \log m$  where m = Number of data inputs, and n = Number of select lines.

• Implementation of one MUX using another MUX:

| Given<br>MUX | To be Implemented<br>MUX | Required Number<br>of MUX |

|--------------|--------------------------|---------------------------|

| 2 × 1        | 4 × 1                    | 3                         |

| 2 × 1        | 8 × 1                    | 7                         |

| 2 × 1        | 16 × 1                   | 15                        |

| 2 × 1        | 64 × 1                   | 63                        |

| 2 × 1        | 256 × 1                  | 255                       |

| $2 \times 1$ | $2^n \times 1$           | $(2^{n}-1)$               |

| Given        | To be Implemented | <b>Required Number of</b> |

|--------------|-------------------|---------------------------|

| MUX          | MUX               | MUX                       |

| 2 × 1        | 4 × 1             | 3                         |

| 4 × 1        | 16 × 1            | 4 + 1 = 5                 |

| $4 \times 1$ | 64 × 1            | 16 + 4 + 1 = 21           |

| 8 × 1        | 64 × 1            | 8 + 1 = 9                 |

| 8 × 1        | 256 × 1           | 32 + 4 + 1 = 37           |

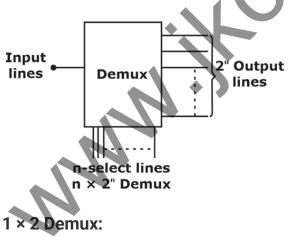

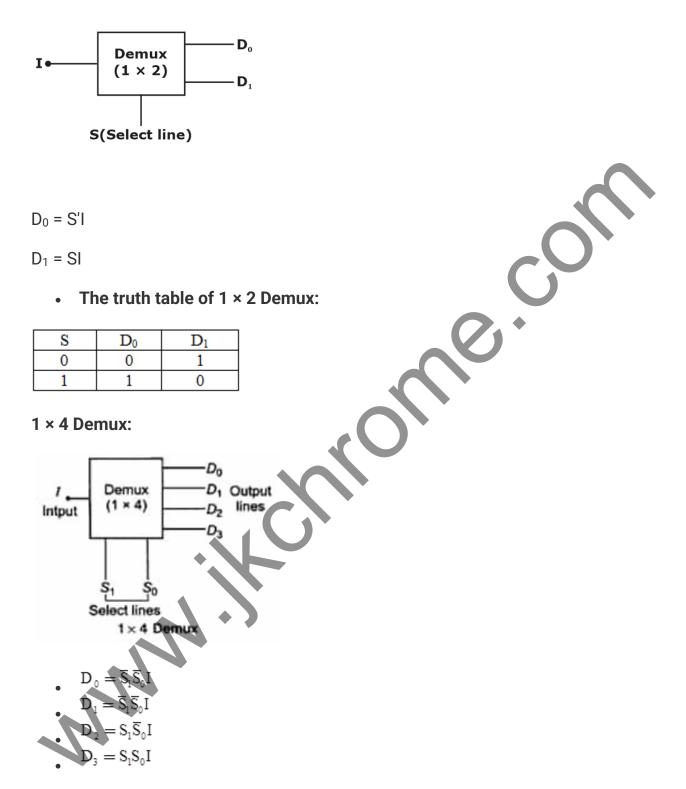

#### 4. Demultiplexer (DEMUX)

- It is a circuit that receives information on a single line and transmits this information on one of 2<sup>n</sup> possible output lines.

- The selection of a specific output line is controlled by the bit values of *n* selected lines.

• The Truth table of 1 × 4 Demux:

| Input | Select Lines | Output Lines      |

|-------|--------------|-------------------|

| I     | $S_1 S_0$    | $D_0 D_1 D_2 D_3$ |

| Ι     | 0 0          | 1 0 0 0           |

| Ι     | 0 1          | 0100              |

| Ι     | 1 0          | 0010              |

| Ι     | 1 1          | 0 0 0 1           |

• Circuit Diagram of 1 × 4 Demux:

Circuit diagram for output lines  $D_0$ ,  $D_1$ ,  $D_2$  and  $D_3$

DEMUX Implementation using another DEMUX:

| Given<br>DEMUX               | To be<br>Implemented<br>DEMUX | Required<br>Number of<br>DEMUX |

|------------------------------|-------------------------------|--------------------------------|

| $1 \times 2$<br>$1 \times 2$ | 1 × 4                         | 3                              |

| $1 \times 2$<br>$1 \times 2$ | 1 × 16                        | 15                             |

| 1×2                          | 1 × 64                        | 63                             |

| $1 \times 2$                 | $1 \times 2^n$                | $(2^{n}-1)$                    |

| 1×4                          | 1 × 6                         | 2                              |

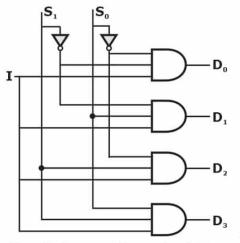

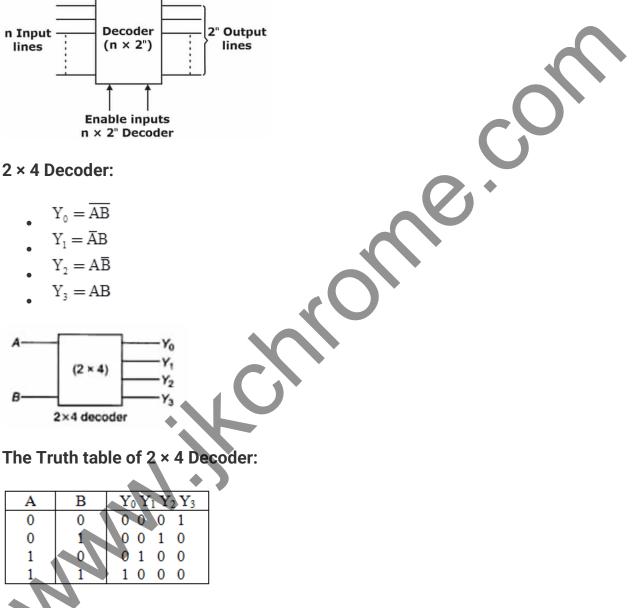

#### 5. Decoders

• A *decoder* is a combinational circuit that converts binary information from *n* input lines to maximum 2n unique output lines.

- If the *n*-bit decoded information has unused or don't-care combinations, the decoder output will have fewer than 2<sup>*n*</sup> outputs.

- The decoders presented here are *n*-to-*m*-line decoders, where  $m \le 2^n$ . Their purpose is to generate the  $2^n$  (or fewer) minterms of *n* input variables.

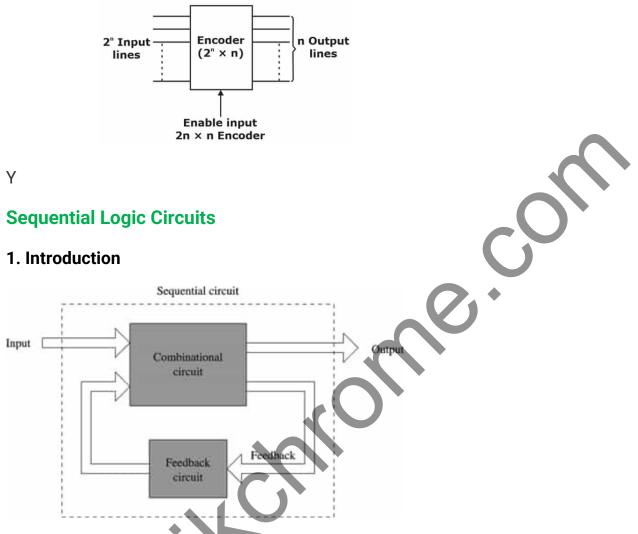

#### 6. Encoders

- It is a combinational circuit that converts information into the coded form (binary).

- It is a digital circuit that performs the *inverse* operation of a decoder.

- An encoder has 2<sup>n</sup> (or fewer) input lines and *n* output lines.

- The output lines generate the binary code corresponding to the input value.

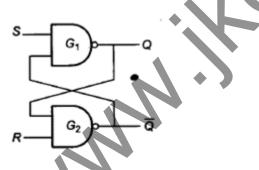

The sequential circuit is of two types.

- **Synchronous Sequential Circuit:** Change in input signals can affect memory elements only upon activation of clock signals.

- Asynchronous Sequential Circuit: Change in input signals can affect memory elements at any instant of time. These are faster than the synchronous circuit.

# 2. Flip Flops

- It is a one-bit memory cell which stores the 1-bit logical data (logic 0 or logic 1).

- It is a basic memory element.

- The most commonly used application of flip flops is in the implementation of a feedback circuit.

- As a memory relies on the feedback concept, flip flops can be used to design it.

- In the synchronous sequential circuit, Memory elements are clocked flip flops and generally edge triggered.

- In the asynchronous sequential circuit, Memory elements are unclocked flip flops/time delay elements which are generally level triggered.

- Flip flop circuit is also known as bistable multivibrator or latch because it has two stable states (1 state, 0 states).

For the electronic circuits, there are mainly four types of flip flops present

- S-R Flip Flop (Basic Flip Flop)

- Delay Flip Flop (D Flip Flop)

- J-K Flip Flop

- T Flip Flop

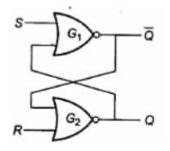

#### **Basic SR Flip Flop**

- The Set-Reset (SR) flip flop is designed with the help of two NOR gates or two NAND gates.

- SR Flip Flop is also called as SR latch.

# SR Latch Implementation Using NAND Gates:

Logic diagram of SR latch using NAND gates

| S | R | Q              |

|---|---|----------------|

| 0 | 0 | Invalid        |

| 0 | 1 | 1              |

| 1 | 0 | 0              |

| 1 | 1 | Previous state |

Truth Table of Logic Diagram

#### SR Latch Using NOR Gates:

Logic diagram of SR latch using NOR gates

| S | R | Q              |

|---|---|----------------|

| 0 | 0 | Previous state |

| 0 | 1 | 1              |

| 1 | 0 | 0              |

| 1 | 1 | Invalid        |

#### Truth Table of Logic Diagram

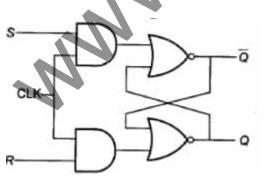

#### Clocked SR Flip Flop Implementation using NAND Gates:

It is also called a Gated S-R flip flop. The main problem with S-R flip flops is using NOR and NAND gate in the invalid state. By using a bistable SR flip-flop this problem can be overcome. This can change outputs when certain invalid states are met, regardless of the condition of either the Set or the Reset inputs.

• SR Flip Flop Using NOR Gates:

SR flip flop using NOR gates

| Clock | S | R | Q                    |

|-------|---|---|----------------------|

| 0     | × | × | Qn                   |

| 1     | 0 | 0 | $Q_n \to Hold$       |

| 1     | 0 | 1 | $0 \rightarrow Hold$ |

| 1     | 1 | 0 | $1 \rightarrow Hold$ |

| 1     | 1 | 1 | Invalid              |

Truth Table of SR Flip Flop

With both S=1 and R=1, the occurrence of a clock pulse causes both outputs to momentarily go to 0. When the pulse is disabled (removed), the state of the flip-flop become indeterminate, depending on whether the set or reset input of the flip-flop remains at 1 longer than the transition to 0 at the end of the pulse.

Characteristic Table

| _      |        |          |                 |                                       |

|--------|--------|----------|-----------------|---------------------------------------|

|        | S      | R        | Qn              | <b>Q</b> <sub>n + 1</sub>             |

| ſ      | 0      | 0        | 0               | 0                                     |

|        | 0      | 0        | 1               | 1                                     |

|        | 0      | 1        | 0               | 0                                     |

|        | 0      | 1        | 1               | 0                                     |

|        | 1      | 0        | 0               | 1                                     |

|        | 1      | 0        | 1               | 1                                     |

|        | 1      | 1        | 0 🔷             | ×                                     |

|        | 1      | 1        | 1               | ×                                     |

| $\sim$ | haract | eristion | equation        | • • • • • • • • • • • • • • • • • • • |

| C      | maract | ensue    | equation        | or six nip n                          |

|        | 9      | = S      | + R Q           |                                       |

|        |        |          | _ <b>_</b> _    |                                       |

| 4      |        | tate     | Prešen<br>state | t                                     |

**Excitation Table**

| Qn | <b>Q</b> <sub>n + 1</sub> | S | R |

|----|---------------------------|---|---|

| 0  | 0                         | 0 | × |

| 0  | 1                         | 1 | 0 |

| 1  | 0                         | 0 | 1 |

| 1  | 1                         | × | 0 |

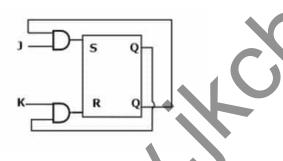

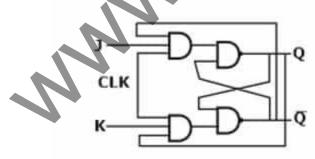

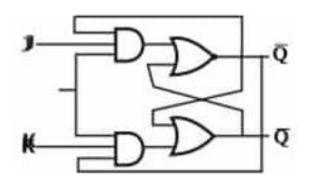

# JK Flip Flop

A JK flip-flop eliminates the indeterminate state of the SR type. Inputs J and K is similar to the inputs S and R to set and clear the flip-flop (In JK flip-flop, the letter J is set and the letter K is for clear). When logic 1 are applied to both J and K inputs simultaneously, the flip-flop switches to its complement state. If Q=1 then it switches to Q=0 and vice versa.

R = KQ

• JK flip flop using NAND latch:

JK flip flop using NOR latch: •

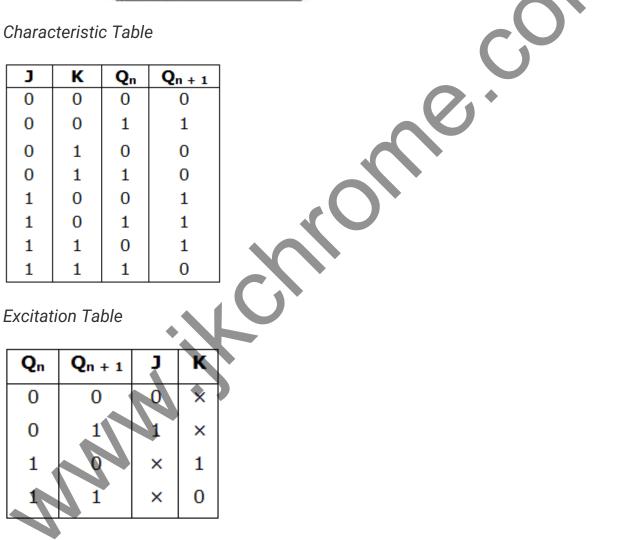

Characteristic Table

Characteristic equation for JK flip flop: •

$$Q_{n+1} = J\overline{Q}_n + \overline{K}Q_n$$

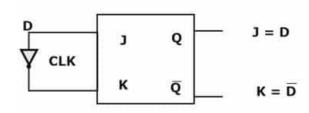

**D-Flip Flop**

D flip flop is also known as a Transparent latch, Delay flip flop or data flip flop. The D input goes directly to the S (J) input and the complement of the D input goes to the R (K) input.

www.jkchrome.com

- The D-flipflop has only a single data input (D).

- If D = 1, the flip-flop is switched to the set state (unless it was already set).

- If D = 0, the flip-flop switches to the clear state.

Truth Table

| Clock | D | <b>Q</b> <sub>n + 1</sub> |

|-------|---|---------------------------|

| 0     | × | $Q_n \leftarrow Memory$   |

| 1     | 0 | 0 ← Reset                 |

| 1     | 1 | $1 \leftarrow Set$        |

Characteristic Table

| D | Qn | $Q_{n+1}$ |  |

|---|----|-----------|--|

| 0 | 0  | 0         |  |

| 0 | 1  | 0         |  |

| 1 | 0  | 1         |  |

| 1 | 1  | 1         |  |

Excitation Table

| Qn | <b>Q</b> <sub>n + 1</sub> | D |

|----|---------------------------|---|

| 0  | 0                         | 0 |

| 0  | 1                         | 1 |

| 1  | 0                         | 0 |

| 1  | 1                         | 1 |

# Characteristic equation for D-flop flop

$Q_{n+1} = D$

# T – Flip Flop

- The T flip-flop is a single input version of the JK flip-flop where T is connected to both J and K inputs directly.

- When T = 0, the flip flop enters into **Hold** mode, which means that the output, Q is kept the same as it was before the clock edge.

- When T = 1, the flip flop enters into **Toggle** mode, which means the output Q is negated after the clock edge, compared to the value before the clock edge.

|          | _         | J                                | Q     |         |    | Ø | • |

|----------|-----------|----------------------------------|-------|---------|----|---|---|

|          |           | к                                | Q     | <u></u> | .( |   |   |

| ruth Tal | ole       |                                  |       | X       |    |   |   |

| Clock    | Т         | Q <sub>n</sub>                   | + 1   |         |    |   |   |

| 0        | ×         | $Q_n \to Me$                     | emory |         |    |   |   |

| 1        | 0         | $Q_n \rightarrow H_{\mathbf{Q}}$ | bld   |         |    |   |   |

| 1        | 1         | $Q_n \rightarrow T c$            | ggle  |         |    |   |   |

|          | 2n        | c Table<br>Qn + 1                | + )   | )       |    |   |   |

| 0        | 0<br>1    | 0 1                              |       |         |    |   |   |

| 1        | 9"  <br>1 | 1<br>0                           |       |         |    |   |   |

**Excitation Table**

| Qn | <b>Q</b> <sub>n + 1</sub> | Т |

|----|---------------------------|---|

| 0  | 0                         | 0 |

| 0  | 1                         | 1 |

| 1  | 0                         | 1 |

| 1  | 1                         | 0 |

• The characteristic equation of T-Flip Flop:

$Q_{n+1} = T \bigoplus Q_n$

#### • Race Around Condition:

- The race around condition will occur in JK flip flop when J = K = 1and  $t_{pd (FF)} < t_{pw}$ .

- $_{\circ}$  To avoid race around condition.

$t_{pw} < t_{pd (FF)} < T_{CLK}$

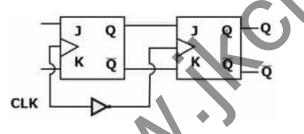

# 3. Master Slave (MS) Flip Flop

• A master-slave flip-flop is constructed from two separate flip-flops. One circuit serves as a **master** and the other as a **slave**. Input clock is applied to master and Inverted clock applied to slave.

- In Master Slave, flip flop output is changed only when slave output is changing.

- The master flip-flop is enabled on the positive edge of the clock pulse and the slave flip-flop is disabled by the inverter.

- The information at the external J and K inputs is transmitted to the master flip-flop.

- When the pulse returns to 0, the master flip-flop is disabled and the slave flip-flop is enabled. The slave flip-flop then goes to the same state as the master flip-flop.

- Master is level triggered, and Slave is edge triggered

- No race around condition occurs in Master Slave flip flop.

- It stores only one bit.

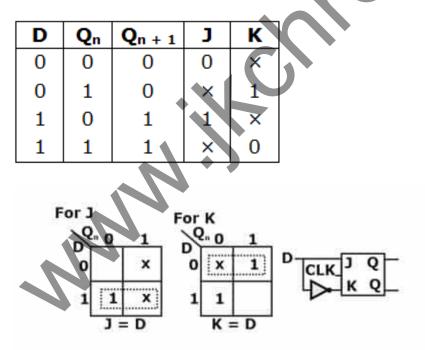

# 4. Flip Flop Conversions

The flip flop conversions are classified into different types which are:

- SR-FF to JK-FF Conversion

- JK-FF to SR-FF Conversion

- SR-FF to D-FF Conversion

- D-FF to SR-FF Conversion

- JK-FF to T-FF Conversion

- JK-FF to D-FF Conversion

- D-FF to JK-FF Conversion

# Procedure for Flip Flop conversion:

- 1. Conversion Table: Construct the characteristic table of required flip flop (unknown), and fill available (known) flip flop excitation.

- 2. Solve K map for given (known) flip flop as input and required flip flop as output.

- 3. Implement the required flip flop using the known flip flop.

# Example: Conversion from JK flip flop to D flip flop is shown below.

#### Characteristic Table

| JK to D                                                     | JK to T                  | JK to SR         |

|-------------------------------------------------------------|--------------------------|------------------|

| $J = D, K = \overline{D}$                                   | J = K = T                | J = S            |

|                                                             |                          | K = R            |

| SR to JK                                                    | SR to D                  | SR to T          |

| $S = J \overline{Q}$                                        | S <u>= D</u>             | S = TQ           |

| R = KQ                                                      | $R = \overline{D}$       | R = TQ           |

| D to SR                                                     | D to JK                  | D to T           |

| $\mathbf{D} = \mathbf{S} + \mathbf{\overline{R}}\mathbf{Q}$ | $D = JQ + \overline{K}Q$ | D=T⊕Q            |

| T = JQ + KQ                                                 | T = SQ + RQ              | $T = D \oplus Q$ |

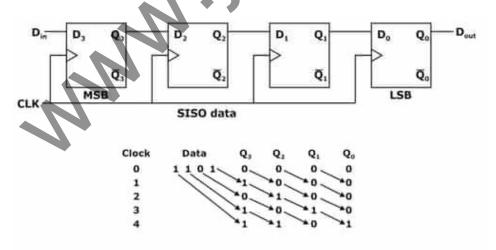

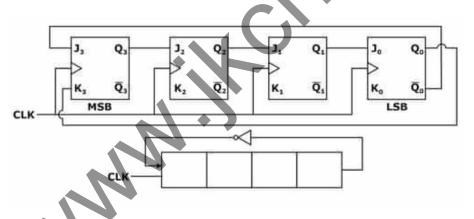

#### 5. Registers

When a group of the flip flop is used to store a word (a group of bits) then it is called register. To store *n* bits, *n* flip flops are cascaded in the register. If in a register, the binary information can be moved from stage to stage, this type of registers is called shift registers. According to data movement in a register, *shift registers can be classified* as

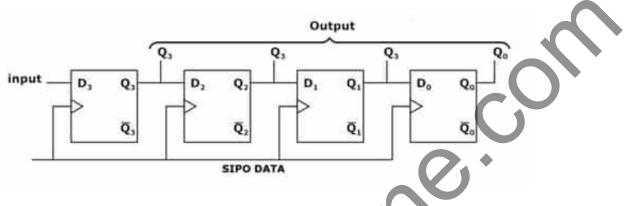

- Serial Input Serial Output (SISO)

- Serial Input Parallel Output (SIPO)

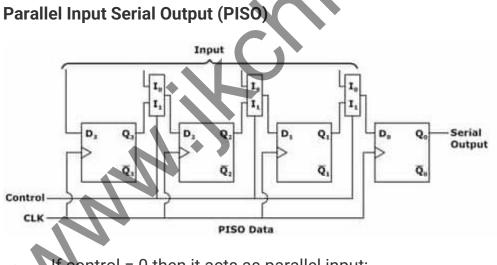

- Parallel Input Serial Output (PISO)

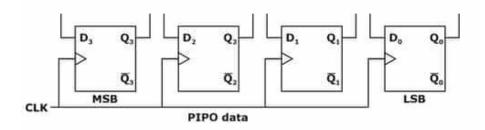

- Parallel Input Parallel Output (PIPO)

# Serial Input Serial Output (SISO)

- In registers edge trigger circuit used to make circuit synchronous.

- If no clock is applied then get same data which is stored.

- In N bits SISO registers to provide N bits data, **Serially in** require N clock pulse, and **Serially out** require (N-1) clock pulse.

# Serial Input Parallel Output (SIPO)

- To provide N-bit data: **Serial in** requires N clock pulse, and Parallel **out** requires no clock pulse.

- SIPO can provide  $n \times t_{CIK}$  delay to the input.

- SIPO can convert serial data or temporal code to parallel or serial code.

- If control = 0 then it acts as parallel input;

- If control = 1 then it acts as serial output;

- To provide parallel input, one clock pulse is required.

- To provide N bits serial output, it requires (N-1) clock pulse.

- PISO can convert special code to temporal code.

# Parallel Input Parallel Output (PIPO)

- In PIPO register for parallel input number of pulse required is 1 clock pulse.

- In PIPO register for parallel output number of pulse required is 0 clock pulse.

- PIPO register cannot be used as a shift register.

- It is used for temporal storage of data in microcontroller, DSP, CPU etc.

#### Summary of Registers

| Type of<br>Register | Number of Pulses<br>Required for Storage<br>of n-bits Input | Number of Pulses<br>Required to n-bit<br>Output |

|---------------------|-------------------------------------------------------------|-------------------------------------------------|

| SISO                | n                                                           | n - 1                                           |

| SIPO                | n                                                           | 0                                               |

| PISO                | 1                                                           | <b>n</b> – 1                                    |

| PIPO                | 1                                                           | 0                                               |

# 6. Counter

- A counter is a sequential logic circuit capable of counting the number of clock pulses arriving at its clock input.

- The sequence of count may be ascending, descending or non-sequence.

- For a counter circuit having *n* flip flops, Maximum possible states (N) = 2<sup>n</sup>

- If N = 2<sup>n</sup>, the counter acts as a binary counter.

- If  $N < 2^n$ , the counter the non-binary counter.

- It counter is capable to count from 0 to 2<sup>n</sup>-1.

- MOD number is the Number of states present in a counter is known as modulus count or MOD number.

• For n-flip flops, the counter will have 2<sup>n</sup> different states then this counter is said MOD- 2<sup>n</sup> counter.

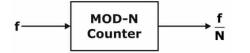

# **MOD-N Counter**

• MOD number indicates frequency division obtained from the last flip flops.

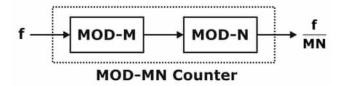

Cascaded two counters:

- MOD-MN counter:

- Overall states of combined counter = MN

- Input frequency = f

- Output frequency f = f/(MN)

#### 7. Classification of Counters

Based upon the applying clock pulse, counters are classified into two categories.

- Synchronous counter

- Asynchronous counter (ripple counter)

| Synchronous Counter                           | Asynchronous Counter                                |

|-----------------------------------------------|-----------------------------------------------------|

| All flip flops are triggered with same clock. | Different clock is applied to different flip flops. |

| It is faster.                                 | It is lower                                         |

| Design is complex.                            | I Design is relatively easy.                        |

| Decoding errors not present.                  | Decoding errors present.                            |

| Any required sequence can be designed.        | Only fixed sequence can be designed.                |

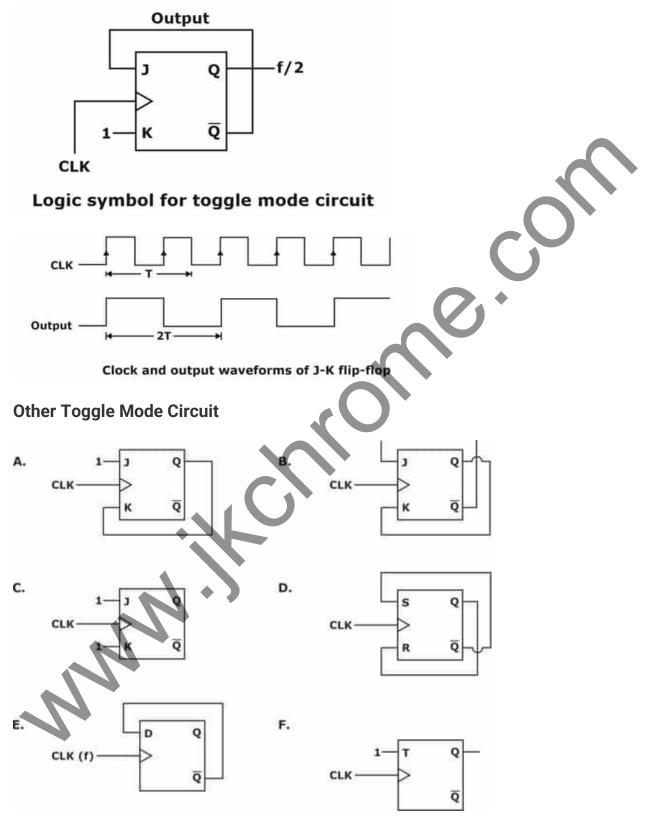

# 8. Toggle Mode Circuit

These are frequency dividers circuit.

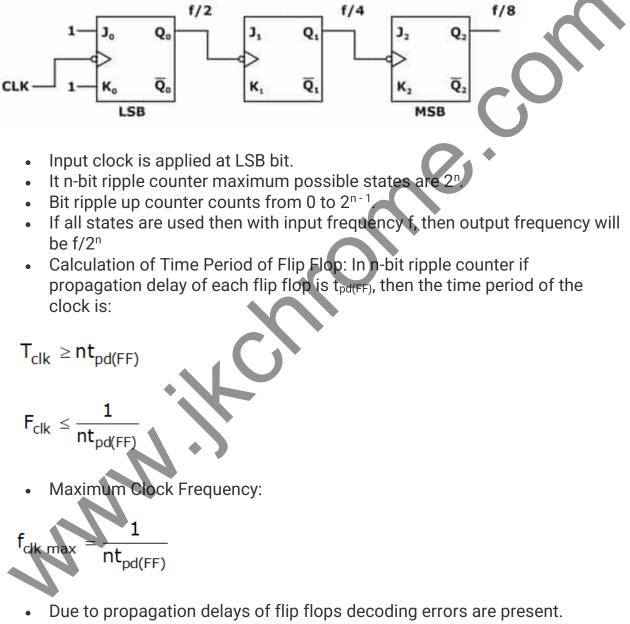

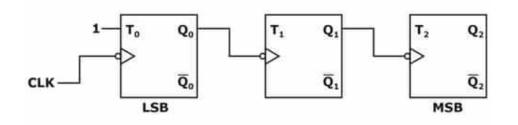

#### 9. Asynchronous Counter (Ripple counter)

- A different clock pulse is applied to different flip flops.

- All flip flops are operating in toggle mode.

- In asynchronous counter flip flop applied with external clock acts as LSB bit.

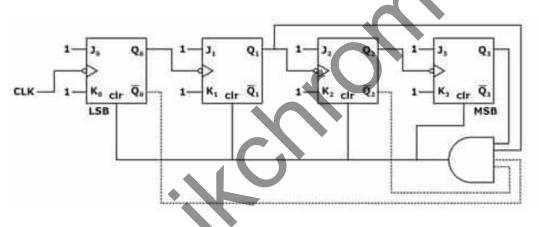

# 3-bit Ripple Up Counter

- Clear and preset are known as asynchronous input to flip flop.

- In any ripple counter, the following conditions will fulfil

- $_{\circ}$  Negative edge trigger and Q as clock  $\Rightarrow$  up counter

- $_{\circ}$  Positive edge trigger and Q as clock  $\Rightarrow$  up counter

#### **3-bit Ripple Down Counter**

- Positive edge trigger and Q as  $clock \Rightarrow down counter$

- Negative edge trigger and Q as clock  $\Rightarrow$  down counter

#### **Non-binary Ripple Counter**

Decode counter or BCD counter is an example of a non-binary counter. It requires 4 flip flops.

- Used state = 10 and unused states =  $6 \rightarrow (2^4 10)$

- Output frequency of BCD counter = f/10

- For making non-binary counter clear (clr) signal is used.

- c1r is active high, and (clr)' is active low.

# **10. Synchronous Counters**

In this type of counter, there are no connections of the first flip flop output to a clock input of the next flip flop.

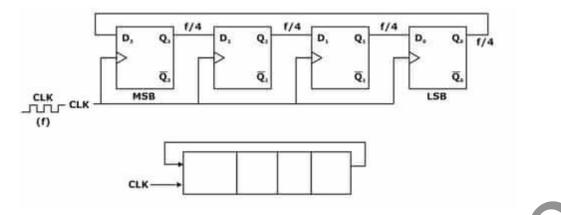

**Ring Counter:** It is a circular shift register with only flip flop being set at any particular time, all others are cleared. It is a shift register with feedback.

- In-ring counter, if the feedback is used the number of states is reduced.

- With n flip flops maximum states = n.

- Number of unused states in-ring counter = 2<sup>n</sup> n

- Maximum Clock Frequency: If the input frequency is f, then at the output of every flip flop we get f/N frequency. In-ring counter, if the propagation delay of each flip flop is  $t_{pd(FF)}$  then

$T_{clk} \ge t_{pd(FF)}$

**Johonson Ring Counter:** Jhonson ring counter is also called as a Twisted ring counter, Switch tail counter, Creeping counter, or Mobies counter.

In n - bit Jhonson counter maximum used states = 2n, unused states = 2<sup>n</sup> - 2n.

- If the input clock frequency is f, the output frequency of each flip flop is f /2n and the duty cycle is 50%.

- A disadvantage of Jhonson Ring Counter: Lockout may occur. To decode each state one, two-input AND or NOR gate is used.

# **Logic Family**

# 1. Integrated Circuits

- Integrated circuits (ICs) are chips, pieces of semiconductor material, that contain all of the transistors, resistors, and capacitors necessary to create a digital circuit or system.

- The first ICs were fabricated using Ge BJTs in 1958.

- o Jack Kirby of Texas Instruments, Nobel Prize in 2000

- Robert Noyes of Fairchild Semiconductors fabricated the first Si ICs in 1959.

#### Integration Levels:

- SSI Small scale integration [12 gates/chip]

- MSI Medium scale integration [100 gates/chip]

- LSI Large scale integration [1K gates/chip]

- VLSI Very large scale integration [10K gates/chip]

- ULSI Ultra large scale integration [100K gates/chip]

#### Moore's Law:

• A prediction made by Moore (a co-founder of Intel) in 1965: "... a number of transistors to double every 2 years."

# Characteristics of digital circuits

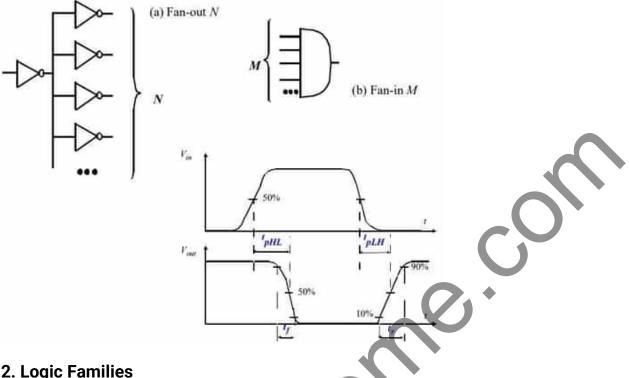

- Fan in:

- Fan in is the number of inputs connected to the gate without any degradation in the voltage level.

- Fan out:

- Fan out specifies the number of standard loads that the output of the gate can drive without impairment of its normal operation

# • Power dissipation:

Power dissipation is a measure of power consumed by the gate when fully driven by all its inputs.

# Propagation delay:

- Propagation delay is the average transition delay time for the signal to propagate from input to output when the signals change in value. It is expressed in ns.

- Noise margin:

- It is the maximum noise voltage added to an input signal of a digital circuit that does not cause an undesirable change in the circuit output. It is expressed in volts.

#### 2. Logic Families

Logic families are sets of chips that may implement different logical functions but use the same type of transistors and voltage levels for logical levels and for the power supplies. These families vary by speed, power consumption, cost, voltage & current levels. The most widely used families are:

- DL (Diode-logic)

- DTL (Diode-transistor logic)

- RTL (Resistor-transistor logic) •

- TTL (Transistor -transistor logic) •

- ECL (Emitter-coupled logic) •

- MOS (Metal-oxide semiconductor) •

- CMOS (Complementary Metal-oxide semiconductor)

# 3. Digital IC Terminology

#### Voltage Parameters:

- V<sub>IH</sub>(min): high-level input voltage, the minimum voltage level required for a logic 1 at an input.

- V<sub>IL</sub>(max): low-level input voltage •

- V<sub>OH</sub>(min): high-level output voltage •

- V<sub>OL</sub>(max): low-level output voltage •

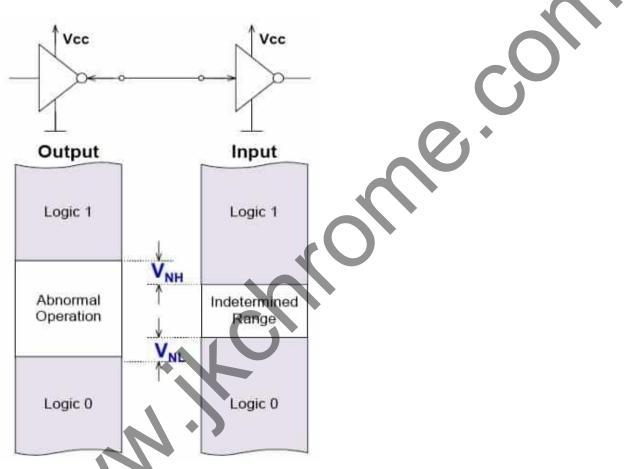

• For proper operation, the input voltage levels to a logic must be kept outside the indeterminate range. Lower than VIL(max) and higher than VIH(min).

#### Noise Margin:

• The maximum noise voltage that can be tolerated by a circuit is termed its noise immunity (noise Margin)

# **Current Parameters:**

IOH – Current flowing into an output in the logical "1" state under specified load conditions

- Current flowing into an output in the logical "0" state under specified load conditions

- I<sub>IH</sub> Current flowing into an input when a specified HI level is applied to that

input

I<sub>IL</sub> – Current flowing into an input when a specified LO level is applied to that input

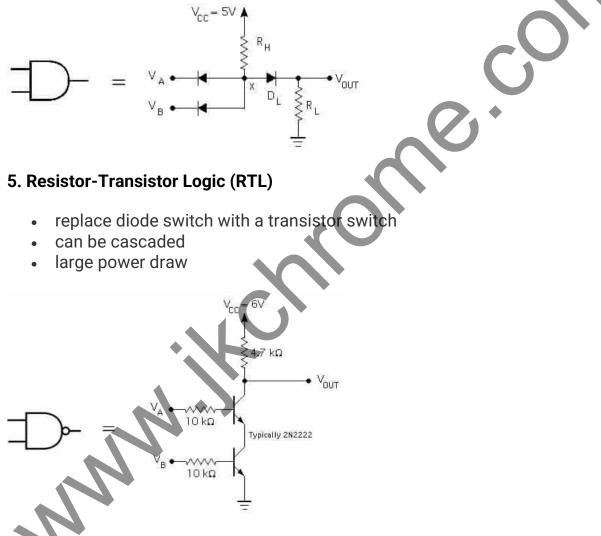

# 4. Diode Logic (DL)

- simplest; does not scale

- NOT not possible (need an active element)

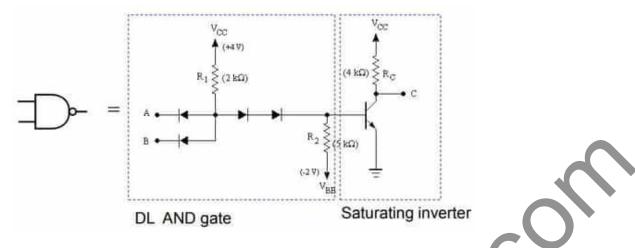

- 6. Diode-Transistor Logic (DTL)

- essentially diode logic with transistor amplification

- reduced power consumption

- faster than RTL

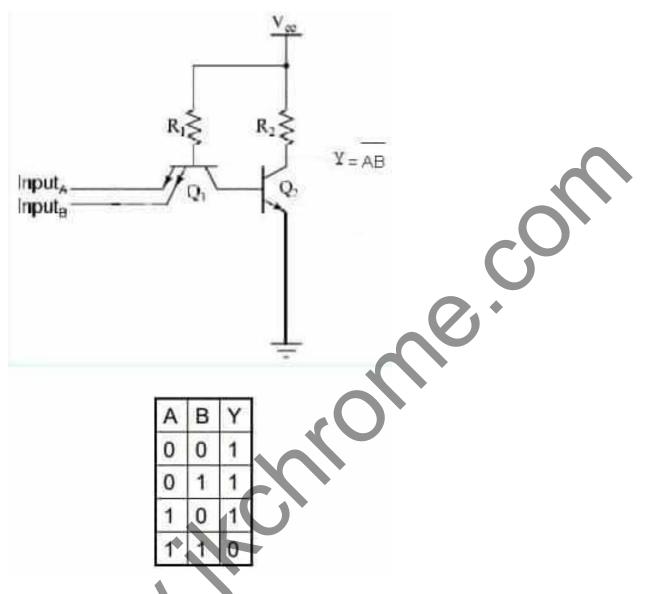

#### 7. Transistor-transistor logic (TTL)

- based on bipolar transistors one of the most widely used families of smalland medium-scale devices – rarely used for VLSI

- typically operated from a 5V supply

- typical noise immunity about 1 1.6 V

- many forms, some optimised for speed, power, etc.

- High-speed versions comparable to CMOS (~ 1.5 ns)

- low-power versions down to about 1 mW/gate

# TTL NAND Gate:

- Input terminals: The emitter of  $Q_1$

- Output terminals: collector of Q<sub>2</sub>

- When any input = logic '0'

- Q1 emitter junction is forward biased.

- Also, its collector junction is FB,

- so Q1 goes in saturation.

- Base of Q2 is at Low voltage

- This causes base-emitter junction of Q2 to be RB, so Q2 goes in cutoff

- Hence output is 5V or logic '1'

When all inputs = logic '1'

- Q1 emitter junction is RB.

- so Q1 goes in cut-off.

- Its collector voltage increases

- This forward biases Q2,

- $_{\circ}$  so Q2 goes into saturation

- Hence output is 0V

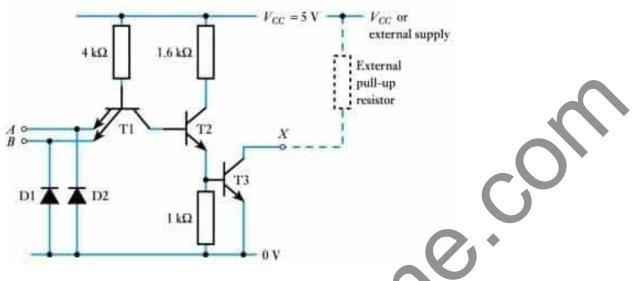

#### A TTL NAND gate with open collector output:

- Its similar to the previous circuit.

- Q2 is used as an emitter follower. The output of Q2 is fed to the input of Q3. Collector of Q2 and Q3 are in phase.

This circuit needs an external 'Pull- up' resistor between output and power supply.

- •

- The disadvantage of open- collector gate is their slow switching speed.

- •

- The pull-up resistance is few kilo ohms. Gives a relatively long time constant, when multiplied by the stray output capacitance.

• Is worst when output goes from low to high.

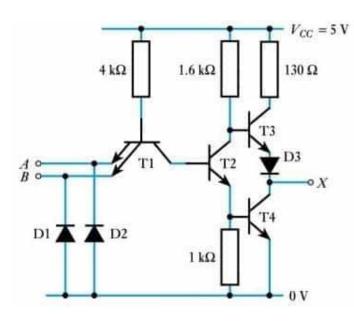

#### TTL NAND gate with totem pole (active pull-up)

- In this circuit Q1 and the 4KΩ resistor act like a 2 input AND gate. The remaining circuit acts like an inverter. Transistors Q3 & Q4 form a totempole <u>i.e.one</u> NPN transistor in series with another.

- With a totem-pole output stage either Q3 or Q4 is on. When Q3 is 'on' output is high. When Q4 is 'on' output is low. If A or B is low, the Q1 conducts and the base voltage of Q2 is almost zero.

- Q2 cuts off, hence Q4 goes into cut off. Q3 base is high, Q3 acts as an emitter follower, the output Y' is high.

- If A and B are high, Q1 does not conduct (cut-off), Q2 base goes high (saturation). Q4 goes into saturation hence output is low.

- The drop across Diode D3 keeps the base emitter diode of Q3 reverse biased. Hence Q3 is off or else it conducts slightly when output is low.

- Now only Q4 conducts when output is low. Totem pole transistors produce a low output impedance. When Q3 is conducting the output impedance is approx 70 Ω. When Q4 is saturated the output impedance is only 12 Ω.

Hence the output impedance of a totem pole circuit is low.

- Any stray output capacitance is rapidly charged or discharged through the low output impedance. Hence the output can change quickly from one state to the other.

#### Types of TTL:

- Standard TTL

- typical gate propagation delay of 10ns and a power dissipation of 10 mW per gate, for a power-delay product (PDP) or switching energy of about 100 pJ

- Low-power TTL (L)

- slow switching speed (33ns)

- reduction in power consumption (1 mW) (now essentially replaced by CMOS logic)

- High-speed TTL (H)

- o faster switching than standard TTL (6ns)

- but significantly higher power dissipation (22 mW)

- Schottky TTL (S)

- used Schottky diode clamps at gate inputs to prevent charge storage and improve switching time. A Schottky diode has a very low forward-voltage drop of 0.15–0.45V approx (silicon diode has a

- voltage drop of 0.6–1.7V). This lower voltage drop can provide higher switching speed.

Faster speed of (3ns) but had higher power dissipation (19 mW) *w-power Schottky TTL (LS)*

used the higher resistance values of low-power TTL and the Schottky diodes to provide a good combination of speed (9.5ns) and reduced power consumption (2 mW), and PDP of about 20 PJ.

# 8. Emitter-coupled logic (ECL)

- based on bipolar transistors, but removes problems of storage time by preventing the transistors from saturating

- very fast operation propagation delays of 1ns or less

- high power consumption, perhaps 60 mW/gate

- low noise immunity of about 0.2-0.25 V

- used in some high-speed specialist applications, but now largely replaced by high-speed CMOS

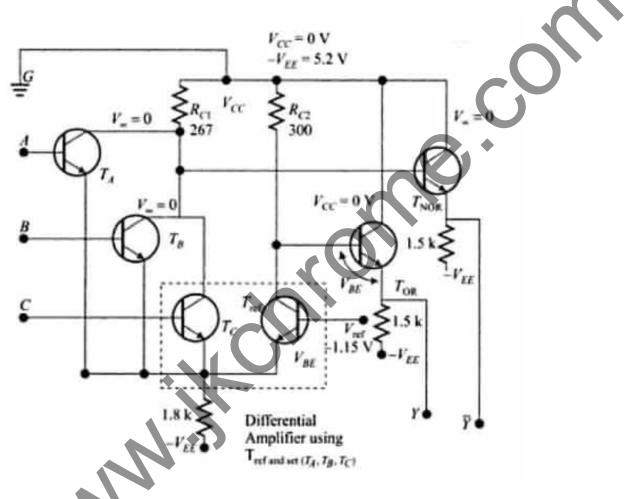

#### Input:

- Input is at the base of the transistor. The emitter of  $T_{ref}$  and input

- transistors couples together. [Hence the name]

- ECL basic gate is OR/NOR gate

- If any input is not connected, the transistor Ti base-emitter will be at cutoff. Therefore, it will be taken as low logic level

Output:

- The outputs ( $T_{OR}$  and  $T_{NOR}$ ) are taken from the emitters of each transistor. The collector of  $T_{OR}$  and  $T_{NOR}$  connects to GND in the CC amplifier mode (also called emitter-follower mode).

- The emitter gives the output, which also connects to -V\_{EE} through a resistance R (~1.5k\Omega)

# Differential Amplifier:

- There is transistor T, which forms a differential amplifier pair between T and the parallel circuits of  $T_A$ ,  $T_B$ ,  $T_C$ . T gets the input reference voltage ( $V_R = -1.15V$ ) from a reference supply circuit.

- The pairs amplify the difference of base voltage of  $T_A$  (or  $T_B$  or  $T_C$ ) and  $V_{ref}$ .

- The emitters of the differential amplifier pairs connect through a common resistance  $R_E$  (~1.8k $\Omega$ ) and to the  $-V_{EE}$ (~ -5V)

# Emitter Follower (CC) amplifier:

- The collectors of (T<sub>A</sub>, T<sub>B</sub>, ... ) are also common.

- Common- collectors of the differential amplifier pairs connect through a resistance RC ( $\sim 267\Omega$ ) to the GND

#### Working:

- Consider  $T_C$  and  $T_{ref}$

- Case 1: let all  $V_{in}$  = -1.6V. But  $V_{ref}$  = -1.15V, so  $V_{in}$  is low and  $V_{ref}$  logic high, So  $T_C$  is in cutoff and  $T_{ref}$  in normal inverting mode.

- $\circ$  So T<sub>OR</sub> gets -1.15V, i.e logic LOW, it is cut off and Y=-V<sub>EE</sub> (LOW)

- Case 2: If  $V_{in}$  at  $T_C$  is -0.7V (HIGH),  $V_{ref} = -1.15V$  (LOW).

- $_{\odot}$  T\_c is in normal inverting mode and T\_{ref} is in the cutoff. –V\_{EE} is reflected at T\_{NOR}.

- So  $T_{NOR}$  is cut-off. Y' = -V<sub>EE</sub> (i.e logic Low).

- Tor is ON, so Y=0v (LOW)

# ECL features:

- Faster speed (2 ns propagation delay) of operation than TTL (10 ns), 74S TTL(3 ns)

- More power dissipation (50 mW/gate) than TTL (10 mW), 74S (19mW)

- Noise Margin at '1'or '0'output and input = 0.4V (- 1.7V and 1.4V)

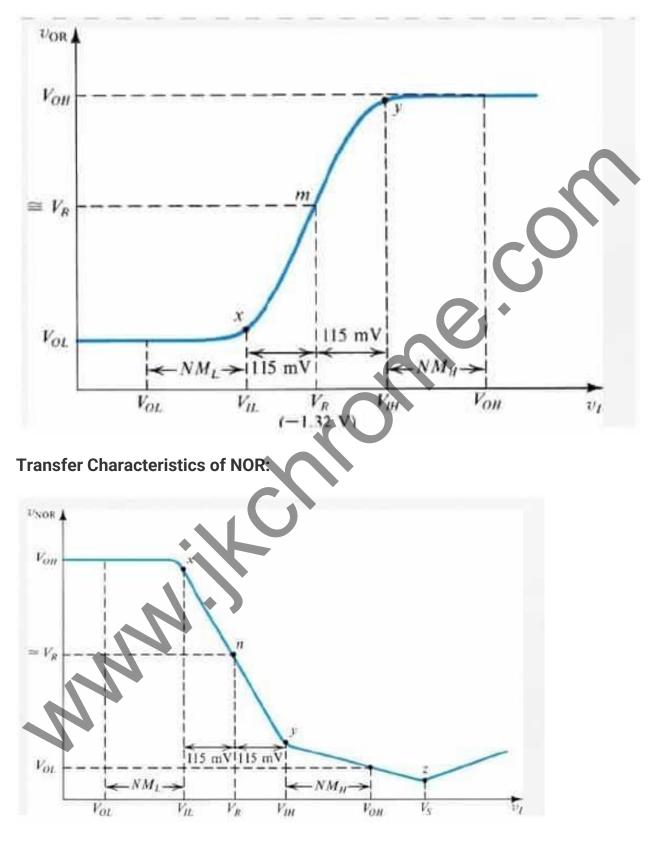

#### Transfer Characteristics of OR:

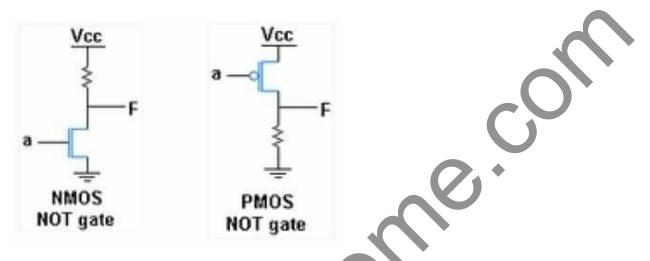

#### 9. MOS inverter

- nMOS Inverter:

- when a='1', nMOS conducts, so F='0'

- When a='0', nMOS is cut-off, so F=Vcc=logic '1'

- pMOS Inverter:

- when a='1', pMOS is cut-off, so F='0'

- When a='0', pMOS is on, so F=Vcc=logic '1'

#### Advantages and Disadvantages of MOS inverter

- Advantage:

- o only a single type of transistor, So, it can be fabricated at low cost.

- Disadvantage:

- as current flows through the resistor in one of the two states, more power consumption is their processing speed is slow

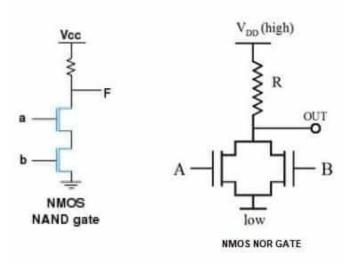

#### NAND and NOR with nMOS

| nMOS NAND                                                                    | nMOS NOR                                                      |

|------------------------------------------------------------------------------|---------------------------------------------------------------|

| When any input is 'O'                                                        | When any input is '1'                                         |

| <ul> <li>corresponding of MOS is off,<br/>So F=V<sub>cc</sub>='1'</li> </ul> | <ul> <li>Corresponding MOS is on, So<br/>F=Gnd='0'</li> </ul> |

| When both inputs are '1'                                                     | When both inputs are '0'                                      |

| • Both MOS is on. F = Gnd = '0'                                              | <ul> <li>Both MOS are off. Out = VDD =<br/>'1'</li> </ul>     |

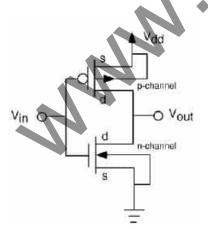

#### 10. Complementary metal oxide semiconductor (CMOS)

- most widely used a family of large-scale devices combines high speed with low power consumption usually operates from a single supply of 5 15 V

- excellent noise immunity of about 30% of the supply voltage

- High fan-out: can be connected to a large number of gates (about 50)

- CMOS gates have equal no.of pMOS and nMOS

- CMOS inverter has a very high input resistance

#### CMOS inverter:

- Upper is pMOS, lower nMOS.

- When V<sub>in</sub> = HIGH, Lower MOS on, V<sub>OUT</sub> =LOW

- When V<sub>in</sub> = LOW, Upper MOS on, V<sub>out</sub> = Vd = HIGH

Advantages of CMOS:

- This configuration greatly reduces power consumption since one of the transistors is always off in both logic states.

- Processing speed can also be improved due to the relatively low resistance compared to the nMOS-only or pMOS-only type devices.

- High Fan-out (usually 50)

- excellent noise immunity

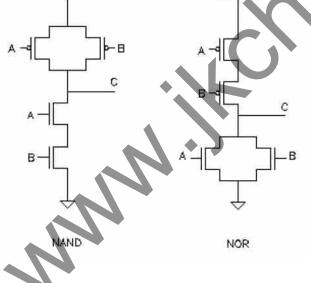

# NAND and NOR with CMOS

| CMOS NAND                                                                                                                              | CMOS NOR                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| If A='1' and B='1'                                                                                                                     | If A='0' and B='0'                                                                                                          |

| <ul> <li>Upper parallel nMOS is off, lower</li> </ul>                                                                                  | <ul> <li>Upper series nMOS is on, lower</li> </ul>                                                                          |

| series pMOS are on, so C=Gnd='0'                                                                                                       | parallel pMOS are off, so $C=V_{dd}='1'$                                                                                    |

| If any A or B or both are '0'                                                                                                          | If any A or B or both are '1'                                                                                               |

| <ul> <li>Upper (any or both) parallel nMOS is<br/>on, lower series(any or both) pMOS<br/>are off, so C= V<sub>dd</sub> ='1'</li> </ul> | <ul> <li>Upper (any or both) series nMOS is<br/>off, lower parallel (any or both)<br/>pMOS are on, so C= GND='0'</li> </ul> |

|                                                                                                                                        |                                                                                                                             |

11. Logic families: Comparison

|                        | TTL       | ECL               | CMOS              |

|------------------------|-----------|-------------------|-------------------|

| Base Gate              | NAND      | OR/NOR            | NAND/NOR          |

| Fan-in                 | 12-14     | >10               | >10               |

| Fan-out                | 10        | 25                | 50                |

| Power dissipation (mW) | 10        | 175               | 0.001             |

| Noise Margin           | 0.5V      | 0.16V<br>(lowest) | 1.5∨<br>(Highest) |

| Propagation Delay (ns) | 10        | <3<br>lowest      | 15<br>Highest     |

| Noise immunity         | Very good | good              | excellent         |

#### **Data Converters**

**DAC and ADC:** It is possible to convert the analog signal to digital and *vice-versa*. We can get analog from digital through DAC and can get digital from analog through ADC.

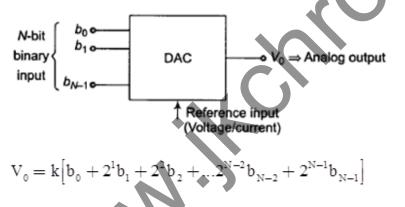

**Digital to Analog Converter (DAC):** D/A converter (also called a DAC) accepts an n-bit digital word and produces an analog sample.

where, k = Proportionality factor,  $b_n$  = 1; if nth bit of digital input is 1,  $b_n$  = 0; if nth bit of digital input is 0.

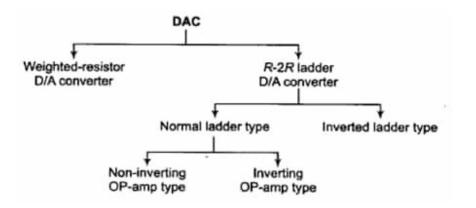

Classification of DAC:

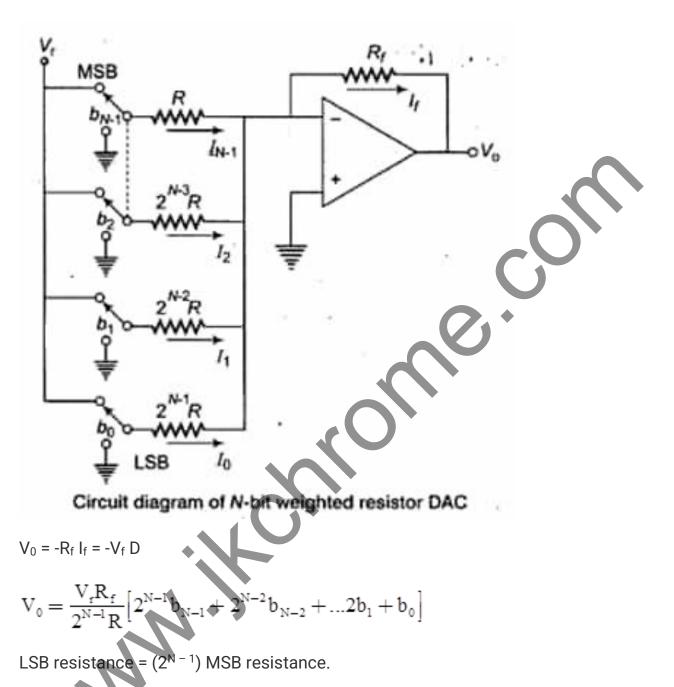

#### Weighted Resistor DAC (N - bit):

- A DAC can be constructed by using a Summing Amplifier and a set of resistors R, 2R, 4R, 8R, etc as its inputs.

- The circuit consists of a reference voltage V<sub>f</sub>, N binary-weighted resistors R, 2R, 4R, 8R, . . . ,  $2^{(N-1)}$  R, N single-pole double-throw switches, and an Opamp together with its feedback resistance R<sub>f</sub> = R/2.

- The switches are controlled by an N-bit digital input word D.

$$D = \frac{b_1}{2^1} + \frac{b_2}{2^2} + \dots + \frac{b_N}{2^N}$$

- The accuracy of the DAC depends critically on the accuracy of the Reference voltage, the precision of the binary-weighted resistors, and the perfection of the switches.

- A disadvantage of the binary-weighted resistor network is that for a large number of bits (N > 4) the spread between the smallest and largest resistances becomes quite large. This implies difficulties in maintaining accuracy in resistor values.

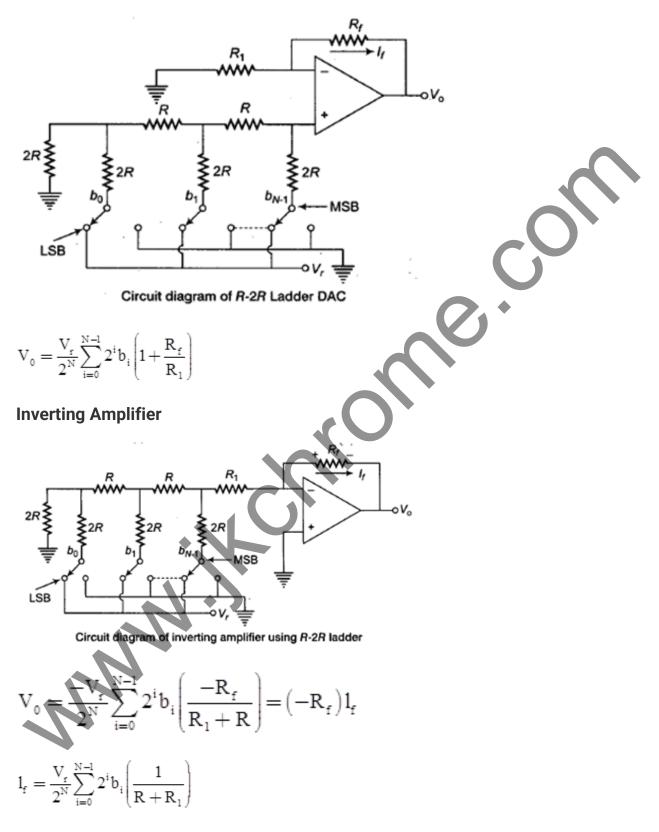

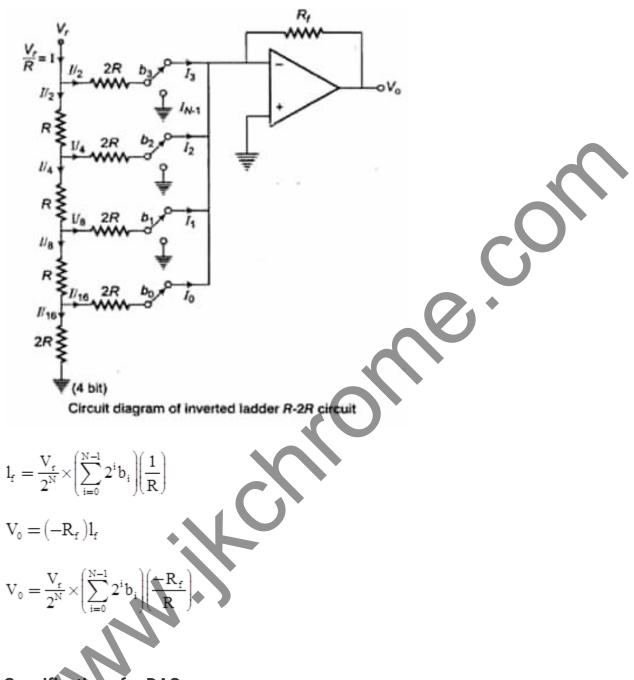

**R – 2R Ladder DAC:** Non-Inverting OP-amp type DAC

Inverted Ladder R – 2R Circuit

#### Specifications for DAC:

- Resolution in DAC is changed in analog output with corresponding to 1 LSB bit increment at the input.

- Resolution = weight of LSB =

- V= Voltage corresponding to logic *N* = Number of bits.

- Analog Output Analog output = resolution x decimal equivalent of binary data

• Maximum Analog Output Voltage (V<sub>FS</sub>) V<sub>FS</sub> is the maximum analog output voltage of DAC.

$$V_{FS} = \frac{V_r}{2^{N-1}} \times (2^{N-1}) = V_r$$

$V_{FS} = V_r$

Percentage Resolution:

$$%R = \frac{1}{2^{N} - 1} \times 100$$

- Maximum Error Maximum error acceptable in ADC and DAC equals to resolution.

- Resolution (R-2R ladder type)

#### Analog to Digital Converter:

- A/D converter (also called an ADC) accepts an analog sample V<sub>A</sub> and produces an N-bit digital word.

- Examples of ADC usage are digital volt meters, cell phone, thermocouples, and a digital oscilloscope.

- Types of A/D Converters: Dual Slope A/D Converter, Successive Approximation A/D Converter, Flash A/D Converter, Delta-Sigma A/D Converter, etc.

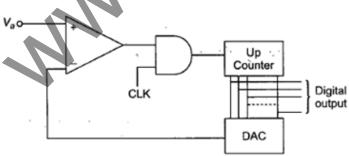

Counter type ADC:

Circuit diagram of Analog to Digital Convertor (ADC)

- In N-bit counter type ADC:

- $_{\circ}$   $\,$  Maximum number of clock pulses required for conversion =  $2^{N}$  -1  $\,$

- $_{\odot}$  Maximum time required for conversion = (2<sup>N</sup> -1) T\_{CLK}

- Minimum number of clock pulses = 1

- Average number of clock pulses = 2<sup>N-1</sup>

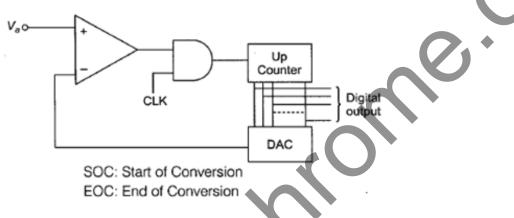

# Successive Approximation Type ADC:

- It is faster than digital ramp ADC.

- Conversion time (t\_c) is independent of the value of the analog input voltage (V\_a).

- It has fixed conversion time.

- Maximum number of clock pulses = N for conversion

- Maximum conversion time = N.T<sub>CLK</sub>

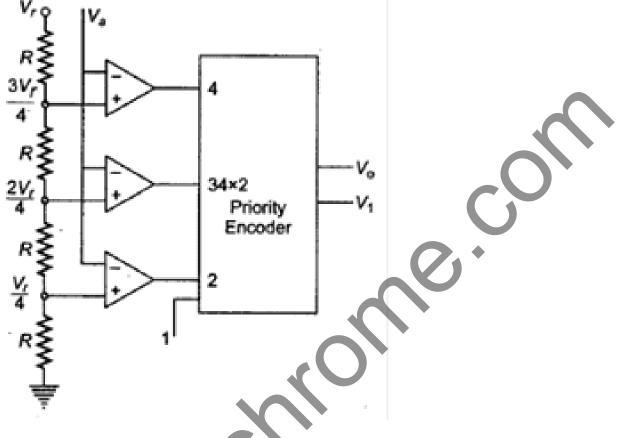

# Flash Type ADC:

- It is also known as Parallel-comparator type ADC or Simultaneous converter.

- It is highest speed ADC (fastest ADC)

- Functional component

- It utilizes 2<sup>N</sup> -1 comparators to compare the input signal level with each of the 2<sup>N</sup>-1 possible quantization levels.

The outputs of the comparators are processed by an encoding-logic block to provide the N bits of the output digital word.

- Complete conversion can be obtained within one clock cycle.

- For N-bit comparator:

- $_{\odot}$  Total number of comparators = 2<sup>N</sup> -1,

- $_{\circ}$  Total number of resistors = 2<sup>N</sup>,

- $_{\circ}$  Total number of priority encoders = 1 (2<sup>N</sup> × N)

#### 2-bit Flash Converter:

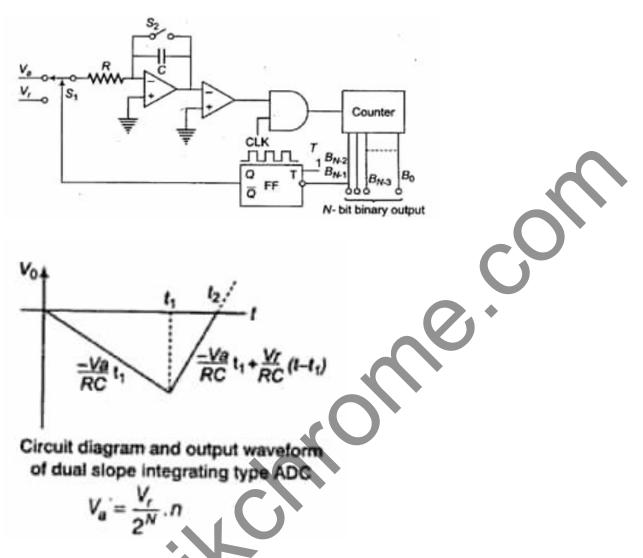

#### **Dual Slope Integrating Type ADC:**

- It has slowest conversion time but has relatively low cost.

- The following components are present in the Dual slope A/D converter:

- Integrator

- Electronically Controlled Switches

- Counter

- Clock

- Control Logic

- Comparator

where, *n* = Count recorded in the counter.

# **Dual Slope Integrating Type ADC:**

- •

- Total number of clock pulses =  $2^{N} + n$ Maximum number of clock pulses =  $2^{N} + 2^{N} 1 = 2^{N+1} 1 = 2^{N+1}$ •

| Type of ADC  | Maximum<br>Number of<br>Clock Pulses | Feature      |

|--------------|--------------------------------------|--------------|

| Counter type | 2 <sup>N</sup> - 1                   | -            |

| SAR          | N                                    |              |

| Flash        | 1                                    | Faster       |

| Dual slope   | $2^{N} + 1$                          | Most acurate |

# JK Chrome | Employment Portal

# Rated No.1 Job Application of India

Sarkari Naukri Private Jobs Employment News Study Material Notifications

JK Chrome

www.jkchrome.com | Email : contact@jkchrome.com